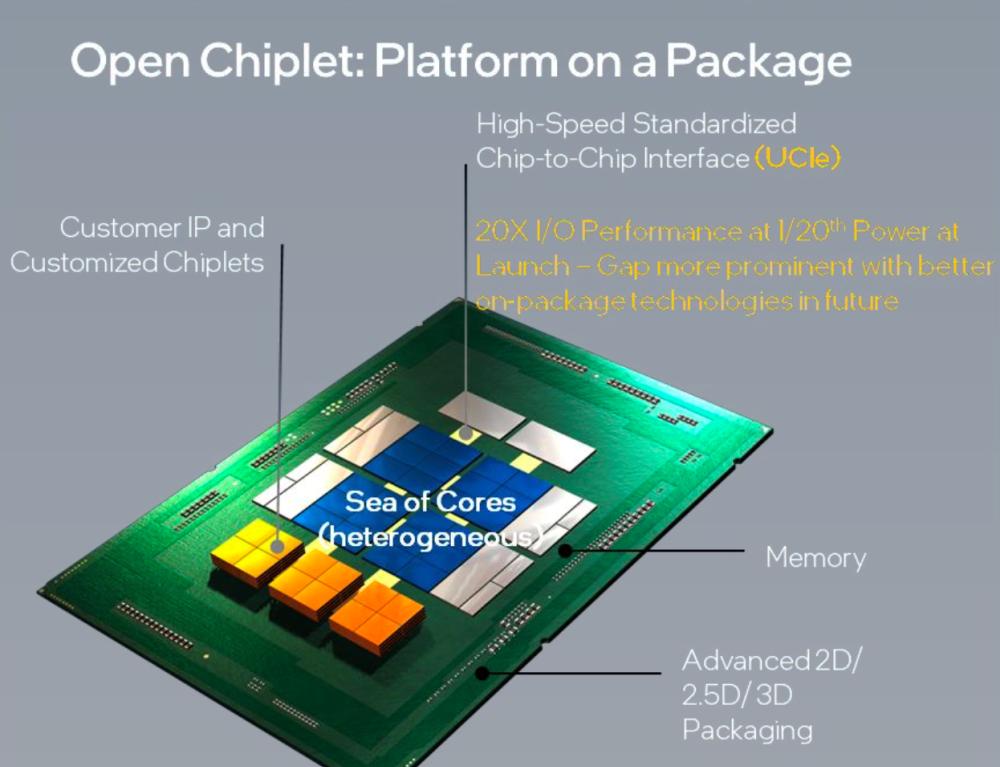

The advanced packaging of heterogeneous integration has undoubtedly become one of the most important engines to promote the development of the semiconductor industry in the post-Moore era. Chiplet-based design methods have proven to be very suitable for the design and implementation of super-large computing power chips and engineering practice methods, AMD, Intel, AWS and other industry leaders have adopted Chiplet technology on their data center CPUs to achieve mass production, and Apple's latest M1 Ultra design also adopts the Chiplet concept. In this context, on March 2 this year, Intel, AMD, Arm, Qualcomm, Microsoft, Google, Meta, TSMC, Sun Moonlight, Samsung and other ten industry giants officially established the Universal Chiplet Interconnect Express (UCIe) industry alliance to jointly promote the standardization of chiplet interface specifications.

A month later, Chinese mainland the first batch of semiconductor companies to join the UCIe Alliance were also announced, including VeriSilicon and Chaomo Technology. For this giant game, what kind of reaction should domestic manufacturers make? Do they have the opportunity and how do they participate in the Chiplet ecosystem?

How do domestic semiconductor manufacturers view Chiplet and UCIe alliances?

As an important application of advanced packaging technology, Chiplet has become another path to achieve performance upgrades under the process microfilm approaching the limit and high manufacturing costs, and is expected to be one of the breakthroughs in China's semiconductor industry under the limited development of advanced processes.

VeriSilicon is one of the earliest enterprises in China to carry out chiplet-related technology research and development. Dai Weimin, founder, chairman and president of VeriSilicon, pointed out in an interview with Aijiwei that Chiplet is expected to solve four major industrial development problems, such as the unsustainable Moore's Law; the significant increase in the design cost and complexity of advanced process chips; more diversified market demand, shortened innovation cycle and continuously improved demand for customized chips at the application side.

For the domestic semiconductor industry, Chiplet also brings many opportunities for them to participate in advanced and cutting-edge chip technology. He pointed out that, first of all, the chip design link can reduce the threshold of large-scale chip design; secondly, veriSilicon, a company with rich IP and leading design capabilities, can exert its own value to a greater extent, upgrade the semiconductor IP licensing business to chiplet business, expand its own technical value at the same time, but also effectively reduce the design cost of chip customers, especially can help system manufacturers, Internet manufacturers such as enterprises that lack chip design experience and resources, develop their own chip products; finally, Domestic chip manufacturing and packaging factories can expand their business scope and enhance the value of enterprises, especially when the development of high-end advanced process technology is blocked, and can also participate in the development of cutting-edge technology by providing chiplets based on other process nodes for high-end chips.

It is precisely because Chiplet uses heterogeneous integrated advanced packaging technology to connect the bare chips (die) of different processes or different fabs, and one of the important challenges is that the connection between dies across multiple suppliers and different processes requires an open and unified standard to allow as many upstream and downstream enterprises as possible to participate, thus finally establishing the entire Chiplet ecosystem, which is the original intention of the UCIe Alliance.

Another company that has actively participated in the Chiplet ecosystem, Gao Zhuan, technical director of Chiplet Technology, pointed out that the release of UCIe means that Chiplet has taken a big step towards more application scenarios, both domestically and internationally. Continuing the idea and direction of Moore's Law, Chiplet has unique advantages in performance, power consumption, volume, and degrees of freedom, but there are also many obstacles, such as high cost, lack of standards for interconnection, testing and yield problems, and so on.

"At present, many large chip companies have products based on Chiplet, but most of the interconnection standards are private protocols defined by themselves, that is, at most they can only interconnect their own products, and the Chiplet cores of different manufacturers cannot communicate and combine." Gao Zhuan said that just like the USB interface, if they are private protocols, the USB host interfaces of various manufacturers and various USB devices are incompatible with each other in addition to their own products, which will greatly limit the use of USB. Chiplet is also similar, theoretically unified chiplet interface standards, everyone's chiplet can be interconnected, which will allow a large number of chip companies to participate, to make a variety of functions of chiplet chiplet chiplet, chip integrators can be based on the function and application needs to chiplet core particles for free combination, will promote the opening and prosperity of the entire Chiplet ecology. So from the perspective of the main bottlenecks in the development of Chiplet, the UCIe standard is very meaningful.

"UCIe established an open and unified di-to-die interconnection standard, providing high-bandwidth, low-latency, high-power and high-performance chip package connections, thus realizing the ability to package bare chips from different sources, and opening the process of full commercialization of Chiplet." The head of the core and semiconductor marketing department said.

However, the fact that UCIe announced that the ten initial members did not see the presence of mainland enterprises has caused some concerns in the context of the current global geopolitical conflict, and will it become another "card neck" area of the mainland in the future?

In this regard, Dai Weimin said that the UCIe Alliance has just been established and is growing, in principle, it is free and open, and it has not closed the window for mainland manufacturers. In fact, VeriSilicon has participated in the discussion in the early days of the formulation of the UCIe specification, and some mainland industrial chains are also actively participating in it, and now with the veriser, Chaomo Technology and other manufacturers have successively announced that they have joined UCIe, I believe that there will be new members gradually open. "We should embrace UCIe, an open standard with international reach." He believes that "domestic chips will not and should not only be interconnected with domestic chips, an open agreement, the more participants are conducive to ecological development." ”

The college also agrees with this view, he stressed that whether a standard can be successful, whether it can be recognized and universally used by everyone, depends on whether it is suitable for application scenarios, whether it can solve pain points, and whether it can be recognized by everyone. UCIe is widely concerned, largely because it is jointly released by a number of large companies, and for now, the UCIe specification is more suitable for Chiplet's application scenarios at the software protocol layer and the physical layer.

As an important participant in the domestic semiconductor industry, although EDA and semiconductor IP giant Synopsys Technology did not appear in the first list of the UCIe Alliance, Zhu Yong, deputy general manager of Synopsys China, stressed that the company has been very supportive of various new agreements and specifications in the industry to promote the further improvement of chip performance. "The ten initial members of UCIe can be said to be all customers of Synopsys, so there are different degrees of direct discussion with them in the process of formulating the relevant specifications." He pointed out, "In the case of Moore's Law approaching the limits of physics and cost, and the PPA improvement of SoC single chip encounters bottlenecks, it has become industry consensus to use 2.5D/3D packaging to improve integration, use Chiplet technology to improve yield and reduce costs, and increase I/O density and communication bandwidth between logic computing chips and memory units through closer spacing." In order to enable the Multi-Die SoCs developed by different vendors to achieve interoperability and achieve more efficient interconnection, the establishment of the UCIe Alliance can be said to be the trend of the times. ”

However, Zhu Yong also said that at the current stage, the UCIe Alliance has just released the UCIe 1.0 specification, and it is not yet possible to judge how much it can promote the development of chiplet ecology, and it is too early to assert that it can develop into an ecological alliance.

For example, according to the white paper released by the alliance, UCIe is mainly composed of D2D (die-to-die) adaptation layer, physical layer (including packaging), but the problems of thermal management and low-power design are not involved. The UCIe 1.0 specification selects the well-established PCIe (PCI Express) and CXL (Compute Express Link) interconnect bus standards, primarily for the protocol layer.

Image credit: UCIe white paper

Zhu Yong further pointed out that in order to make Chiplet generalized, UCIe not only needs to define the protocol layer, but also needs to define the standard of the physical layer, but the standard of the physical layer is not so easy to completely unify, including the different processes used by various wafer manufacturers, different technical routes, and the corresponding physical layer stacks are also different. At present, UCIe only defines a scope in the physical layer, and it is not so easy for the industry to achieve complete interconnection. "In a sense, UCIe only defines a grand goal." He believes that "for domestic manufacturers, they should maintain a welcoming attitude, if the standard can be popularized in the future, it is also beneficial for domestic manufacturers to launch their own Chiplet products faster." ”

What areas does Chiplet apply to? Who takes the first step?

Despite its strengths, chiplets also require a good business model to be commercially implemented. Omdia data predicts that the Chiplet market size will reach $5.8 billion by 2024 and more than $57 billion by 2035. In this market that is predicted to take off, there are still only a few industry giants that have the ability to use Chiplet, and what areas will the application prospects of this technology appear in the future?

The head of the core and semiconductor marketing department believes that compared with AI artificial intelligence and HPC high-performance computing, the design scale of chips is the highest, and these two areas will be more urgent to try Chiplet technology, which also explains that Intel, AMD, Arm and other chip manufacturers are the first participants in the UCIe Alliance.

"As you can see, whether it is Intel's Ponte Vecchio processor presented in ISSCC 2022 or the M1 Ultra chip released by Apple not long ago, Chiplet technology is used, and AMD's Chiplet CPU has also proved to be a very successful product." GaoZhuan believes that "from the perspective of domestic enterprises, companies that do high-performance CPUs, GPUs and large AI chips will be the first to use Chiplet technology." ”

Dai Weimin further summarized and predicted the main application prospects of Chiplet, he believes that tablet application processors, autonomous driving domain processors, and data center application processors will be the first application areas of Chiplet to land. "Tablet processors need to integrate heterogeneous processing IP with a variety of different functions, autonomous driving domain processors need to be highly reliable and can be iterated quickly, and data center processors need to integrate a variety of general-purpose high-performance computing modules." He pointed out, "Especially for autonomous driving applications, Chiplet's design methodology can greatly improve the iteration efficiency of automotive chips, reduce the safety hazards that may be caused by the failure of a single chip, and do not need to redesign a large chip and re-take the car specification certification every iteration upgrade, thus improving the time to market and reliability of automotive chips." ”

Image source: VeriSilicon

He also pointed out that not all chips are suitable for chiplets, not split for the sake of splitting; in many cases, a single integrated system chip, such as an Internet of Things system chip based on the FD-SOI process integrated RF wireless connectivity function, will be more valuable. If all the bare cores like the Apple M1 Ultra are "split" by large chips using cutting-edge technology, in fact, there is no reference significance for other manufacturers. "Apple M1 Ultra can be said not a design-for-Chiplet concept, for most general-purpose platforms, it should be different IP modules based on the 5nm to 22nm range of different process of the product architecture planning, through the building block like 'building' to achieve comparable to the performance of the entire chip using advanced processes, that is, do not need to use advanced processes for each module."

More importantly, with no experience to follow, Chiplet vendors and end-application customers are waiting to see who takes the first step, which is a chicken-and-egg question. "Our consideration as an IP vendor and design service provider is who should bear the cost of chiplet's one-time engineering (NRE); the concern of end-application customers is that chiplet products have not been verified, how reliable and cost-effective is it? Are there enough IP modules available? Dai Weimin said, "In this situation of mutual wait-and-see, the upstream chiplet cannot determine the application scenario, and it is impossible to define the chip." ”

However, he also revealed that at present, there are already many chip projects based on advanced processes in the mainland region, and VeriSilicon is actively communicating with companies interested in using Chiplet, and trying to explore the solution of "crowdfunding" Chiplet to potential customers, which is expected to break the deadlock as soon as possible. And if UCIe's specifications can be rapidly promoted under the impetus of industry giants, then domestic projects can immediately follow up.

Zhu Yong added that many domestic star start-ups in the big chip project, will use Chiplet technology, including GPU, AI chip and automatic driving chip, can not bypass chiplet and only rely on the manufacturing process to improve performance, on the one hand, the cost is too high, on the other hand, the yield will not be too good.

How can domestic manufacturers participate in the Chiplet ecosystem?

Chiplet has become a new competition dominated by today's big manufacturers, from what angles can domestic manufacturers cut into this ecosystem? At present, some manufacturers have made positive deployments.

As the no. 1 semiconductor IP supplier in the Chinese mainland, VeriSilicon has six major types of processor IP cores, such as graphics processor IP, neural network processor IP, video processor IP, digital signal processor IP, image signal processor IP and display processor IP, and has leading chip design capabilities, and has been committed to the promotion of Chiplet technology and industry in recent years, and proposed IP chip (IP as a Chiplet, IaaC) and Chiplet as a Platform are two major design concepts.

Dai Weimin explained that IP chip design is to achieve the "plug and play" of special function IP with Chiplet, to solve the balance of performance and cost in advanced processes of 5nm and below, and to reduce the design time and risk of large-scale chips, in this design concept of chip products, ISP, NPU, VPU, GPU and CPU and other computing units and on-chip caches, interfaces, etc. will be based on different process processes. Chip platforming is to create different chip products with different feature sets by adding or removing Chiplets, based on the concept, The original chip originally launched a high-end application processor platform with chiplet architecture design last year, it took only 12 months from definition to tape-out, and the engineering samples were successfully lit on the day of the return, and linux/Chrome OPERATING system, YouTube, Android games and other applications were successfully run in the prototype. The 12nm SoC version of the product is currently undergoing validation work on autonomous driving domain controllers and is undergoing iterations of the Chiplet version. "Over the years, VeriSilicon's efforts in the Chiplet project have not only promoted the industrialization of Chiplet, but also pushed VeriSilicon's semiconductor IP licensing business and one-stop chip customization service business to a new height." Chip original may be the first company in the world to launch Chiplet commercial products for customers. ”

Another ONE-stop supplier of IP/chip customization, ChipLite Technology, believes that Chiplet is very likely to become the mainstream in the field of high-performance large computing power new products, especially for the current breakthrough of the computing power bottleneck of large computing chips such as AI and CPU/GPU, and is also one of the key technologies to solve the problem of "card neck" of wafer process in the process of high-quality development in the mainland. The company also took the lead in launching China's independent standard Innolink Chiplet technology in 2020, and successfully implemented the technology for the first time in its first domestic high-performance 4K graphics card GPU chip "Fenghua No. 1" released last year, doubling the performance by connecting the two GPUs.

GaoZhuan said that Chiplet Technology has been working in the field of Chiplet interconnection technology for many years, and has launched three Chiplet interconnection technologies of Innolink A/B/C, which have been used in products to support the heterogeneous implementation of high-performance CPU/GPU/NPU chips. "What's more, the Innolink Chiplet has long been designed with cross-compatibility in mind and has enough versatility. Although the interconnection standards of most large chip companies are proprietary protocols defined by themselves, In the early days, Chippe has cooperated and licensed with many cooperative manufacturers to establish a set of protocol standards that are both inclusive and can be optimized for special efficiency in the professional field. He emphasized, "Benefiting from its versatility and flexible customization, it has obtained a lot of commercial verification, in addition to our own use, but also empowered multiple customers to scale mass production, and we have layouts at multiple process nodes, which can provide customers with one-stop customization." ”

Image source: Chip Technology

It is worth mentioning that in September 2020, As the initiator, Chiplet Technology launched the China Chiplet Industry Alliance together with Academician Yao Zhizhi of the Chinese Academy of Sciences, in order to strengthen the application and promotion of domestic Chiplet technical standards and compatibility with international standards.

"We noticed that there are two specifications in the UCIe specification, standard package and advanced package, and these two specifications are very similar to the ideas and technical architectures of Innolink B and C of Core Motion Technology, which are separately defined IO interfaces for standard packages and advanced packages, which are single-ended signals and forward clocks. Based on Innolink B/C, Chiptron will quickly launch IP products compatible with UCIe's two specifications, empower domestic and foreign chip design companies, and help cooperative chip companies quickly launch Chiplet products that are compatible with UCIe standards. The high commissioner explained.

It should be noted that the EDA design tool also played a cornerstone role in the development of Chiplet. In this regard, the domestic EDA leader jointly released the "3DIC Advanced Package Design Analysis Full Process" EDA platform with Synopsys at the end of August last year, of which Metis is an EDA simulation platform applied to bare chips, 3DIC, Chiplet and advanced package joint simulation, which can be seamlessly integrated with the 3DIC Compiler design environment to form a unique 3DIC design, simulation and verification solution in the industry.

The head of the marketing department of Core and Semiconductor said that the simulation platform allows users to skip the cumbersome configuration of traditional modeling tools and quickly and accurately optimize the simulation design by considering the entire physical environment of the key area; Metis' embedded three-dimensional full-wave high-precision electromagnetic simulation engine MoM Solver can cover the simulation frequency of DC-THz, fully meet the accuracy requirements of high-speed and high-frequency applications in heterogeneous integration, and can perfectly support cross-scale simulation from nanometer to centimeter At the same time, the simulation platform also integrates core core technologies such as core and original Absorbing Fence, Magnetic Current and Mesh Tunneling, which can realize the simulation requirements of ultra-large-scale heterogeneous packaging under the premise of ensuring accuracy.

It has to be admitted that many domestic companies still rely on the "nanny" services of companies such as Synopsys Technology and Arm, especially in the field of Chiplet. Zhu Yong pointed out that even though some design firms may have the resources to develop their own Chiplets and IPs, even larger companies cannot afford to develop all ip in-house, and they may want to procure third-party IP to save time and cost. In the current Die-to-Die interface standards, it mainly includes AIB, OpenHBI, BoW, etc., of which OpenHBI can provide the highest edge density standard, which is very suitable for applications that must transmit extremely high bandwidth between two Chiplets. It can achieve speeds of 8Gbps per pin, a maximum interconnect length of 3mm at maximum data rates, and a power consumption target of less than or equal to 0.5pJ/bit.

In this regard, Synopsys offers a range of Die-to-Die IPs, including high-bandwidth interconnects (HBIs) and SerDes-based PHIs and controllers, among others, and DesignWare HBI PHY IP supports multiple standards, including AIB, BoW and OpenHBI. The IP implements a wide parallel and clock forwarding PHY interface, targeting advanced 2.5D packages to take advantage of finer chip-to-chip connectivity in interposer-based technologies. On the other hand, Synopsys' 3DIC Compiler provides a unified platform for Chiplet integration, providing an integrated ultra-convergent environment for 3D visualization, pathing, exploration, design, implementation, verification and signoff, integrating system-level signal, power consumption and thermal analysis into the same tightly integrated solution.

Zhu Yong stressed that the domestic semiconductor industry chain actively participates in the Chiplet ecosystem, which can not only enhance the original main business, but also provide more breeding services by improving technical strength. "For example, IP companies can provide hard, die-level IP on the basis of traditional soft IP, interface IP, etc.; packaging plants can cut from the traditional pcb package at the substrate level to silicon-level packaging; chip companies can also benefit from modularization and launch application-level chips faster and better." He pointed out, "However, for design companies, it is necessary to have more complex large-chip system architecture planning and design capabilities, from a higher dimension, systematic analysis, design and testing capabilities." This also requires EDA companies such as Synopsys to provide a strong definition of the complete design process and develop supporting design aids to help them improve production efficiency. ”

epilogue

While more domestic manufacturers are joining the UCIe Alliance, we also see that China is intensively deploying its own Chiplet industry specifications. Before the boots land, no one can assert whether the industry should fight its own battle, but there is no doubt that a more open and broad standard is more conducive to the benign development of the industrial ecology.

Chiplet still faces many problems such as design and integration, ecosystem complexity, manufacturing/testing and production, qualification and reliability, standards, etc. For the domestic semiconductor industry chain, only by continuously enhancing its strength in the field of high-performance computing chips, working together to come up with first-class Chiplet products. When our chip products and chip ecology are strong enough, it is possible to participate in the formulation of specifications and even develop more competitive Chiplet standards.

(Proofreading/Mike)