作者 | John Russell

譯者 | Sambodhi

策劃 | 淩敏

在春季 GTC 會議上,英偉達首席科學家兼研究部進階副總裁 Bill Dally 介紹了英偉達研發機構的基本情況,以及目前一些優先事項的細節。Dally 今年将重點放在英偉達正在研發并使用的人工智能工具上,這是一種非常聰明的逆向營銷。比如,英偉達就已經利用人工智能來提高 GPU 的設計效率。

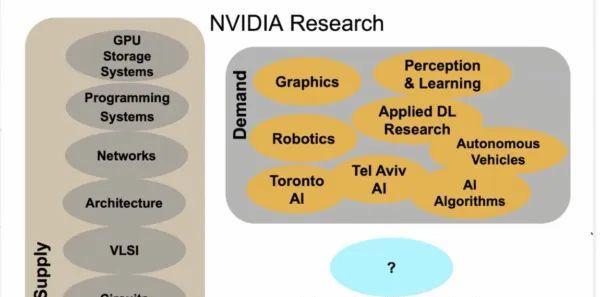

Dally 在今年的演講中稱:“我們有一個 300 人左右組成的小組,嘗試着去預測我們在英偉達産品方面的前景,我們就像是一盞遠光燈,想要把遠處的事物照亮。我們被松散地分成兩半。一半為 GPU 提供技術。它讓 GPU 自身更加完善,包括電路、VLSI 設計、架構網絡、程式設計系統,以及進入 GPU 和 GPU 系統的存儲系統。”

“英偉達研究團隊希望開發出能夠很好地使用 GPU 的軟體系統和技術。我們一直在推動計算機圖形技術,并且有三個不同的計算機圖形研究小組,同時還有五支不同的人工智能小組。現在使用 GPU 來運作人工智能是一項龐大的工程,并且規模不斷擴大。我們還有一個小組專門研究和生産機器人和無人駕駛汽車。”他說,“我們也有一些面向地理位置的實驗室,比如多倫多和特拉維夫人工智能實驗室。”

英偉達有時會從一些小組中挑選一些人來實行瘋狂的計劃,比如有一個小組開發出了英偉達的實時光線追蹤技術。

和以往一樣,Dally 的談話中有一些重複,但是也有一些新的内容。這個小組的規模,當然要比 2019 年大約 175 人有所增長,因為人們對無人駕駛系統和機器人的支援力度越來越大。Dally 說:“一年之前,英偉達把 Macro Pavone 從斯坦福大學挖來,上司他們新的無人駕駛汽車研發小組。”他并沒有過多提及 CPU 的設計,但無疑,這方面的工作也得到了強化。

以下是 Dally 對英偉達在設計晶片時越來越多地使用人工智能的評論的一小部分(略加編輯),并附上了一些支援的幻燈片。

利用圖神經網絡測繪電壓降

“身為一名人工智能專家,我們當然想要利用人工智能來設計更好的晶片。我們有好幾種方法可以這樣做。第一條最簡單的途徑就是我們可以使用(與人工智能相結合)已有的計算機輔助設計工具。比如,我們可以測繪 GPU 裡的電力消耗,并且可以預測栅極電壓會降低到什麼程度——所謂的 IR 下降就是指電流乘以電阻壓降。用正常 CAD 軟體來做這件事要花上三個小時。”Dally 說道。

在 Dally 看來,這是一個疊代的過程,需要做的就是訓練一個人工智能模型,來獲得相同的資料。

“我們在一堆設計上這樣做,基本上就能将功率圖輸入,由此産生的推理時間僅需要三秒鐘。當然,如果把特征提取的時間算在内,這需要 18 分鐘。我們能夠很快地取得成果。在這個案例中,我們采用了圖神經網絡,而不是卷積神經網絡,我們這麼做,就是要估算電路中各個節點的開關頻率,進而促進了前面例子中的功率輸入。”Dally 說,“我們可以在很短的時間内得到精确的功率估算,這要比傳統的方法快。”

利用圖神經網絡預測寄生效應

Dally 表示自己最喜愛的工作之一就是利用圖神經網絡來預測寄生效應。在幾年前,他曾是一名電路設計師。以前,電路設計是一個非常反複的過程,你要繪制一副半導體的原理圖,但是你并不清楚它的性能如何,直到布局設計師拿到這副原理圖,進行了布局,并提取了寄生器件,然後你才能進行電路仿真。

“你會回去修改你的原理圖(并再次通過)布局設計師,這是一個非常漫長的、反複的、非人道的、勞動密集型的過程。現在我們可以做的是通過訓練神經網絡來預測寄生效應,而無需進行布局。這樣,電路設計者可以非常快速地進行疊代,而不必在循環中進行手工布局的步驟。這裡的圖表顯示,與基準真相相比,我們對這些寄生器件的預測非常準确。”

布局和路由的挑戰

Dally 稱,AI 還可以預測路由擁堵情況,這對企業們的晶片布局至關重要。

正常的過程是,研發人員必須采取一個網表,通過布局和路由過程運作,這會非常耗費時間,通常要花上好幾天。雖然能夠了解擁堵情況,但會發現原來的布局還不夠完善。是以必須重新設計,用另一種方法來布局宏,這樣就可以避開那些紅色的區域(如下圖所示)。

這裡有太多的線試圖通過一個特定的區域,有點像交通堵塞的車位。“我們現在能做到的就是不用再進行布局和路由了,我們可以利用這些網表,并且通過圖神經網絡,基本地預測哪裡會出現擁堵,進而達到很高的精準度。”他說,“這還不夠完善,但是它表明了問題所在的區域,我們可以立即采取措施,快速地進行疊代,而無需進行完整的布局和路由。”

标準單元遷移的自動化

Dally 表示,目前這些方法都是通過人工智能對人類的設計進行批判。真正讓人激動的是,将人工智能用于實際的設計。

Dally 舉了個例子,比如 NVCell 系統,該系統采用了模拟退火與強化學習相結合的方法來設計标準單元庫。每獲得一項新技術,比如從 7nm 轉向 5nm,就擁有了一個單元庫。Dally 說:“事實上,我們有數以千計的這種單元,并且必須用一套非常複雜的設計原則在新技術中進行重新設計。”

據 Dally 介紹,英偉達主要利用強化學習來布局半導體。在過去,當半導體被布局好之後,往往會出現大量的設計規則上的錯誤,就像電子遊戲一樣。而這正是強化學習最拿手的。

“在 Atari 電子遊戲中使用強化學習就是很好的範例。這就好比是一款 Atari 電子遊戲,不過它是一款修複标準單元中設計規劃錯誤的電子遊戲。我們可以用強化學習來修正這些設計規則中的錯誤,進而使我們可以在很大程度上實作一個标準單元的設計。”

如下圖所示,92% 的單元庫可以通過這款工具來實作,而不存在設計規則和電氣規則方面的錯誤。此外,還有 12% 的單元要小于人類設計的單元。“總體上來講,在單元複雜性方面,這款工具做出來的單元,與人類設計的單元相當,或者更好。”Dally 表示。

這對英偉達來說有個好處是可以節約很多人力資源。在過去,一個大約 10 人的小組需要花費一年的時間,來完成一個新的技術庫的移植。現在,可以使用多台 GPU 運作幾天來完成。這樣,人類就能處理 8% 未自動完成的單元。“在很多案例中,我們最終能得到更好的設計。這樣可以解決人力,而且優于人類的設計。”

Dally 的演講還有很多關于英偉達研究開發的内容,英偉達的研究和開發主要集中在産品上,而非基礎科學。如果你感興趣的話,也可以了解下 Dally 在 2019 年、2021 年關于英偉達研究開發的演講。看完後你會發現,Dally 在研究開發工作群組織方面的描述并沒有什麼改變,但是主題是不一樣的。

https://www.hpcwire.com/2022/04/18/nvidia-rd-chief-on-how-ai-is-improving-chip-design