AMD began to use TSMC's 7nm process process in 2019, introducing the Zen 2 architecture processor, and the leading position on the process node was one of the most important features of the new product at that time. Thanks to TSMC's N7 process node, AMD is very competitive in both the desktop and enterprise markets. As Intel advances from 14nm to 10nm process, AMD will also move from 7nm to 5nm in the second half of 2022, introducing it into Zen 4 architecture products.

At a ces conference this year, Anandtech asked AMD CEO Dr. Zifeng Su whether the leading process node is the key to maintaining competitiveness for AMD products. Special consideration is given to the input costs of small chip designs and advanced processes.

Dr. Su Zifeng said that AMD is constantly innovating in various fields, and leading small chip design technology helps to integrate them through packaging. At present, AMD has a strong delivery capacity in products using the 7nm process, and has launched products using the 6nm process, followed by the Zen 4 architecture and the 5nm process. AMD has 2D and 3D chip designs and will do so using the right technology. Dr. Su Stressed that the technology roadmap is designed to make the right choice and the right timing, and confirmed that the 5nm process technology used by AMD will be optimized for high-performance computing and will not necessarily be exactly the same as other existing 5nm technologies.

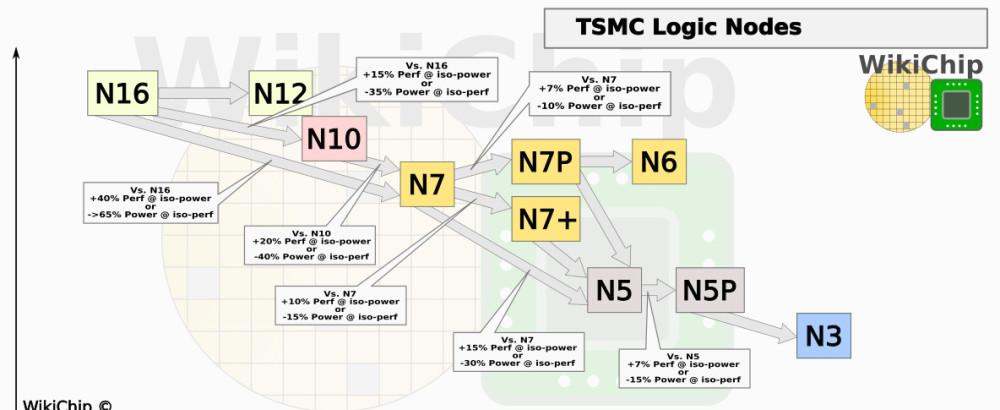

According to AMD, in the era of small chips, the combination and packaging method is becoming more and more important, even more important than what kind of process nodes are simply used. In addition, in order to adapt to the performance needs of different types of chips, wafer foundries will make targeted adjustments on the same process node, and TSMC currently has at least three processes involving N7 process nodes.

It is understood that TSMC has accepted a total of $5.44 billion in advance payments from at least 10 customers, including Apple, AMD, Nvidia and Qualcomm, to ensure future capacity supply.