據台媒聯合報報道,台積電3納米制程今年8月将導入量産,但台積電為取得制霸權,防止英特爾殺出搶單,決定将3納米研發團隊轉戰1.4納米開發,并預定下個月鳴槍起跑,投入确認技術規格的第一階段(TV0)開發,這也為台積電準備跨足1納米世代,揭開曆史新頁。

報道進一步指出,台積電日前敲定于今年8月于竹科研發中心P8廠及南科18B的P5廠,南北同時啟動3納米量産後,接下來要在先進制程開發上壓制英特爾藉由2納米技術突破争食蘋果新世代處理器的威脅,以持續在晶圓代工保持領先優勢。

考慮到三星和英特爾都對台積電嘴邊的蛋糕虎視眈眈。毫無疑問,又一輪晶片制程大賽即将打響。

台積電急了

在之前的财報會上,台積電聯席總裁魏哲家曾經表示,公司的2nm工藝正在研發當中,如按照初步規劃,試産将在2024年底,最快則将于2025年投入量産。但是,英特爾在更早之前曾經表示,公司将在今年下半年完成Intel 18A(約為1.8nm )的晶片設計,并将原定的量産時間從之前的2025年提前到2024年。由此,我們可以看到台積電擔憂的來源。

另一個方面,對工藝制程有了解的讀者應該知道,今年下半年開戰的3nm工藝推進到現在,其實基本面已經定了。因為三大廠商(台積電、英特爾和三星)的工藝進度,甚至客戶在目前看來都初步确定,且短期有太大的變化的可能性比較小。

但在3nm後的技術節點,則又有新的不确定性。

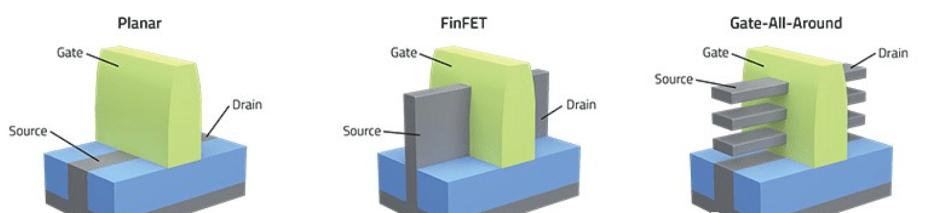

衆所周知,自2011年英特爾釋出22nm工藝以來,包括Intel、台積電、三星、格芯和中芯國際都幾乎在所有的先進工藝邏輯晶片上使用FinFET半導體制造。和以前的平面半導體溝道是水準的不一樣。在 FinFET 中,溝道是垂直的,栅極環繞在溝道周圍,能從溝道的三個側面提供出色的控制。

正因為這種不同尋常的設計,FinFET在應用中帶來了更多的優勢。例如對于給定的半導體占位面積有更高的驅動電流、更高的速度和更低的洩漏,這使其能夠具備更低的功耗、無随機摻雜劑波動,使得半導體具有更好的遷移率和縮放比例。借助這個創新的半導體設計,晶片制造技術演進到了今年下半年面世的3nm。因為除了三星以外,其他晶圓代工廠在這個節點依然使用的是FinFET。

平面半導體、FinFET半導體和GAA半導體

然而,到了3nm以後的工藝,FinFET的曆史使命就已經完成了,這就驅使所有晶圓代工廠就不得不探索新的制造方法,如三星在3nm上應用的GAA(Gate All Around)半導體就是當中一個選擇。和當初從平面往立體轉一樣,新的半導體也會給開發者提出新挑戰。需要提示一下的是,三星在3nm就用上了這種新型半導體,而英特爾也披露了不少關于他們新半導體的資訊,他們更是把Intel 18A看作超越台積電的關鍵技術。再加上,近日日經新聞報道,美國和日本正計劃在2nm晶片上合作。考慮到日本在裝置上的領先、目前的晶片本地制造趨勢、美國IBM過往在先進工藝上的輝煌曆史、熱潮他們也于一年前推出2nm晶片等多種因素。

這就讓在新工藝保密工作做得非常之好的台積電急了。

GAA沒那麼簡單

如上所說,GAA半導體是行業必然的發展趨勢,而納米片就是GAA半導體的首個選擇。

所謂納米片,從構造上看,納米片FET是一種旋轉90度的finFET,這就讓其可以産生水準堆疊的fin,而每個fin中間都有垂直栅極材料,且每個fin都是一個溝道。

Lam Research在其2020年的一篇部落格中介紹道,早期的GAA裝置将使用垂直堆疊的納米片。它們由單獨的水準片構成,四周都被門材料包圍。這提供了相對于finFET改進的通道控制。與更高電流需要多個并排fin的FinFET不同,GAA 半導體的載流能力通過垂直堆疊幾個納米片來增加,栅極材料包裹在通道周圍。納米片的尺寸可以縮放,以便半導體的尺寸可以滿足所需的特定性能。

該篇部落格文章進一步指出,納米片在概念上可能很簡單,但它們對制造提出了新的挑戰。其中一些挑戰圍繞着制造結構,其他涉及實作 PPAC 擴充目标所需的新材料。

如圖所示,GAA半導體是通過首先生長交替的Si和SiGe外延層的超晶格來制造的,這些外延層構成了納米片的基礎。而其關鍵步驟則包括沉積内部電媒體間隔物以保護源極/漏極區域并定義栅極寬度,以及用于去除犧牲層(sacrificial layer)的溝道釋放蝕刻。去除犧牲層後留下的空間需要用栅極電媒體和金屬填充,包括納米片之間。因為栅極金屬很可能會引入新材料,為此一些制造商正在評估钴,钌、钼、鎳和各種合金。

在semiengineering的報道中,他們也揭露了制造納米片FET帶來的重大挑戰。

首先在流程中,外延工具在襯底上沉積超薄、交替的SiGe和矽層,形成超晶格結構。這種結構可能具有三層、五層或更多層的每種材料;其次,微小的垂直fin在超晶格結構中被圖案化和蝕刻。然後,形成内間隔物。在間隔蝕刻中,超晶格結構中的SiGe層的外部部分被凹陷,然後用介電材料填充;第三,形成源極/漏極。然後,去除超晶格結構中的SiGe層,留下構成通道的矽基層或片;最後,通過沉積高k電媒體和金屬栅極材料形成栅極。

”以上每一步都是一個挑戰。與所有工藝一樣,目标是開發沒有缺陷的晶片。這需要在晶圓廠中采用完善的工藝控制政策。”semiengineering的記者在文章中強調。(關于納米片制造,請參考半導體行業觀察的文章《FinFET的繼任者:納米片該如何制造?》)

台積電制造內建經理在今年二月接受IEEE采訪的時候就首先強調,我們正在接近原子尺度。然後他繼續說:“以前,我們可以通過微調工藝來實作下一代節點,但現在每一代我們都必須在半導體架構、材料、工藝和工具方面找到新的方法。在過去,這幾乎是一種主要的光學縮小,但這不再是一個簡單的技巧。”

Lam Research方面則表示,GAA半導體将成為FinFET的繼任者,而納米片将演變為納米線。這些GAA結構應該貫穿目前路線圖上的進階流程節點。

三巨頭各出奇招

正因為新技術擁有如此大的的挑戰,是以三巨頭都在夜以繼日地攻克新制造技術,他們也都先後披露了其面向未來新技術上面做得一些布局。

首先看比較“急”的台積電。在ISSCC 2021上,台積電董事長劉德音做了一個演講,在演講中他大概介紹了一下台積電的納米片技術。劉德音指出,這些新器件的漏極引起的勢壘降低和亞門檻值擺動更小。而根據報道,使用TSMC的下一代平台降低了SRAM的電源電壓,讓其可以在0.46V下提供可靠的緩存操作。而随着對片上高速緩存的需求不斷增加,電壓低于半伏肯定會改善晶片功率預算。

雖然台積電在研讨會上沒有太多披露,但據一些分析師分析,台積電展示的資料來自32 MB SRAM,但沒有給出其他技術細節。他們大膽猜測其M0間距為28 nm,這就像在 5N 工藝中一樣,這是納米片的寬度約為35 nm,厚度約為6 nm。正是這樣的設計為其提供了240–250 nm的溝道寬度,或相當于目前鳍片高度的2+鳍片半導體。

semiwiki在一篇文章介紹,台積電研發組的Jin Cai在去年的VLSI研讨會上開展了一場名為“下一個十年的 CMOS 器件技術”的讨論。在演講中,他透露了台積電主動工藝研發的三個領域,講述獲得更優化納米片特性的方法:分别是增加pFET的SiGe化學計量、優化寄生Cgs/Cgd電容、處理底部納米片的“mesa””洩漏。(具體參考文章《台積電談2nm的實作方式》)。

接下來,我們看一下領先一步的三星。因為他在今年下半年就帶來公司的GAA半導體制造技術,也就是三星在3nm使用的MBCFET(multi-bridge channel FET)制造技術。

三星官方檔案表示,典型的 GAA 半導體采用細長納米線的形式. 然而,溝道需要盡可能寬以允許大量電流流過它,并且納米線的小直徑使得難以獲得這種更高的電流。為了克服這個問題,三星創造了他們專有的MBCFET(多橋通道場效應半導體)并申請了專利。在三星看來,這是GAA半導體的優化版本。通過将導線形成的溝道結構對齊為二維納米片來增加與栅極接觸的面積,MBCFET能夠實作更簡單的器件內建以及增加電流。在三星看來,公司的MBCFET是一種具有競争力的半導體結構,因為它不僅包括通過GAA結構減輕短溝道效應的方法,而且還通過擴大溝道面積來提高性能。

最後,再看一下英特爾的GAA半導體RibbonFET

據介紹,RibbonFET 器件能夠将溝道從基底材料上擡高,形成進入一塊栅極材料的溝道線。由于溝道線的形狀像帶狀,是以新的FET技術被稱為 RibbonFET,而栅極完全圍繞通道。這種獨特的設計顯着提高了半導體的靜電特性,并減小了相同節點技術的半導體尺寸。但這并不是英特爾所做的唯一技術改進;他們還開發了一種新的電源路由技術,稱為PowerVia。傳統的半導體具有形成半導體的平面半導體,然後添加導線層以提供電源和信号。混合電源和信号會帶來路由挑戰,并降低最終裝置的整體效率。

而英特爾新宣布的PowerVia,能将半導體的電源連接配接移動到晶片的底部。簡而言之,PowerVia的引入相當于PCB從單面層轉移到雙面層。讓電源線和信号線可以分開,使兩層都更加高效。

總結

由上可見,無論是台積電、三星還是英特爾,他們其實都已經為GAA做好了充分準備,迎接下一個節點的到來。與此同時,他們還在繼續研發面向未來的工藝,讓晶片的性能提升擁有更多的選擇。如二維材料就是包括台積電在内的晶圓廠的一個努力方向。

據相關研究人員稱,二維半導體有望解決大尺寸半導體中的通道控制問題:減小器件尺寸也會減小溝道長度。界面缺陷(由于半導體栅極溝道的小尺寸)導緻載流子遷移率下降。而MoS2等過渡金屬二硫化物 (TMD) 就是亞10nm溝道半導體的首選材料,因為它們在極薄的厚度下具有高遷移率。

在去年年中,台積電更是公布,公司與麻省理工學院(MIT)共同發表研究,首度提出利用「半金屬铋」(Bi)作為二維材料的接觸電極,可大幅降低電阻并提高電流,使其效能幾與矽一緻,有助實作未來半導體1納米的挑戰。

除了這些晶圓制造龍頭外,IMEC等研究機構在為未來的晶片實作提出了很多方案和改進方式。晶片制造的未來,依然可期。

來源:内容由半導體行業觀察(ID:icbank)原創,作者:穆梓,謝謝。