集微網報道 UCIe聯盟的成立再次讓Chiplet成為熱點。有半導體産業鍊中的頭部玩家背書,Chiplet有望在未來改寫産業的技術走向和商業發展模式。

先進封裝是Chiplet實作過程中的重要一環,決定着晶片的最終成敗,但是該技術的風頭似乎都被晶圓廠所搶占了。那麼,在Chiplet标準的大潮中,獨立封裝企業到底在扮演什麼角色,而大陸封裝業又應該以怎樣的姿态去迎接标準化時代的到來呢?

先進封裝強則Chiplet強

Chiplet概念并非憑空而來,源自于1970年代誕生的多晶片模組,即由多個同質或異質等較小的晶片組成大晶片。當單晶片工藝進展放緩時,Chiplet便承擔了實作平衡晶片功能和生産成本的責任。

在Chiplet走紅之前,一種相似的技術已經開始流行,那就是SiP(System in Package,系統級封裝)。SiP的定義是将多個具有不同功能的有源電子器件與無源器件,以及諸如MEMS或光學器件等組裝到一起,實作一定功能的單個标準封裝件,進而形成一個系統或子系統。

這個解釋與Chiplet非常相似,兩者都是采用封裝技術進行晶片組合,差別究竟在哪裡?

通富微電總裁石磊認為,在廣義的封裝基礎上可将Chiplet視為SiP的一種,因為SiP的範圍非常廣泛,多die,die和被動器件合封都是SiP。“現在提到的Chiplet是強調把超大尺寸die設計成多個中/大尺寸die,再進行晶圓制造和封裝加工,是從細分角度考慮。而通常提及的SiP,最典型的是手機裡的各子產品,其主要特點是把大量小尺寸(及不同功能)的小die和大量的被動器件封裝在一起,主要是強調子產品高內建化。”石磊告訴集微網。

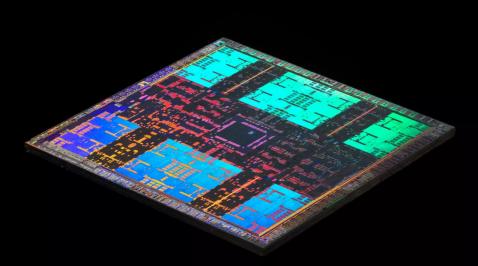

一個典型的Chiplet就是AMD的Zen2架構處理器,其CPU核心與I/O核心分離制造,CPU使用了台積電7nm工藝,I/O則是格芯的14/12nm工藝,兩者最後封裝成單一晶片。

從中也看出了兩者之間的差異。雲天半導體董事長于大全認為Chiplet重在拆分組合,“晶片的功能單元被分出來,然後再重新整合成一個完整功能的晶片,相當于一個物體拆成很多積木,然後又搭成一個新東西出來。”

“可以認為SiP涵蓋了Chiplet的很大部分,但有一部分沒有被考慮。”于大全強調。

在封裝層面,Chiplet還是與SiP有很多相似之處,都采用了大量先進封裝技術。與之相應,封裝層面的挑戰也随之而來。

在石磊看來,Chiplet雖然避免了超大尺寸die,同時也意味着超大尺寸封裝,又高度融合晶圓後道工藝,更在封裝Micro-bump、多layer 扇出FO、超多晶片FC等方面帶來了極限技術挑戰,如封裝加工精度和難度進一步加大,工藝視窗進一步變窄,通用裝置比例降低,裝置更新需求大等。

于大全也認為技術挑戰将加大,“将不同的晶片放在矽interposer(中介層)上,是目前高性能Chiplet的主要選擇,但怎麼把晶片的高速接口連接配接在一起,就需要特定的協定,需要微凸點的制造技術,需要晶片堆疊技術,需要TSV制造技術,這些實作起來很有挑戰性。”

于大全表示:“還有一類廣義的Chiplet,比如把CPU加上memory放在一起,可以用TSV(矽過孔)也可以用Fan out(扇出型封裝)來做,但是對布線的精度要求就很高了,如TSV的布線精度在1μm以下,Fan out的布線技術在2μm左右,這就是Chiplet需要解決的關鍵封裝問題。”

最後一個挑戰在于高可靠性,“因為Chiplet中的晶片變多了,連接配接的點變多了,界面也就變多了,可靠性問題是非常嚴峻的。”于大全特别指出。

除此之外,散熱和功率配置設定也是需要考慮的巨大問題,Chiplet要繼續前進,先進封裝技術還要解決很多挑戰。

封裝廠:機遇與挑戰并存

UCIe聯盟為Chiplet指定了多種先進封裝技術,包括英特爾EMIB、台積電CoWoS、日月光FoCoS-B等。這也折射出一個現實,圍繞先進封裝的競争越來越激烈。

調研機構Yole釋出的《2021年先進封裝行業現狀報告》中指出,雖然OSAT主導着先進封裝市場,在初制晶圓方面OSAT約占整個市場的70%。然而,在高端封裝領域,包括2.5D/3D堆疊、高密度扇出,大型代工廠(如台積電)和IDM(如英特爾和三星)在高端市場發展迅速,占據了市場主導地位。

台積電近年來成為封裝技術創新的引領者,從CoWoS到InFO,再到SoIC,與蘋果、AMD聯手打造多個明星産品,英特爾也在多款産品中運用了自研的先進封裝技術。一時間,前道封裝技術風光無限。是以,很多人自然會質疑OSAT(委外封測代工廠)在Chiplet封裝中逐漸會邊緣化。

封裝廠商并不認可這個觀點。石磊認為:“Chiplet融合了晶圓廠部分中後道技術,是以台積電為代表的晶圓廠推出了封裝解決方案,但Chiplet多數環節還是基于傳統和先進封裝,封裝廠的經驗積累和制造加工也特别重要。同時,晶圓加工注重通用和歸一,而封裝注重客戶個性化需求,能靈活發展各類封裝技術專長,快速提供滿足市場需求的Chiplet産品,封裝廠發展Chiplet是大有可為之處的。”

長電科技對集微網表示,“我們看到這兩三年,前道制造和後道制造,包括設計,都在積極地參與到異構內建,2.5D、3D封裝這樣的一個聯合陣線上來。這反映了一個産業協同向前發展的必然趨勢。前道制造在後前走,後道制造也在向前走的時候,難免中間會出現共通的領域。但大方向毫無疑問是前道制造做前道制造擅長的事情,後道制造做後道制造擅長的事情,最後把Chiplet形成最後的晶片成品,這就肯定還是要由做最後成品的企業來做這件事情。”

“Chiplet變成一個Chip之後,還要做封裝,不管是Fan Out也好,BGA也好,是以像台積電這樣的企業還會找封裝廠合作,因為自己根本封裝不完這麼多晶片,這就給了封裝廠大量的機會。”于大全也持相似觀點。

據一位業内人士判斷,如果等近年來建立晶圓廠都釋放産能後,會有大量加工後的晶圓流向後道封裝廠,是以後道先進封裝市場仍有較大提升空間。

同時,為了和晶圓廠相抗衡,封裝廠也在開發自己的先進封裝技術,如扇出型封裝技術。雖然命名各異,但是各大封裝廠都已經擁有了自己的扇出型封裝技術(請參看《集微咨詢:扇出型封裝正在變得無處不在》一文)。

石磊認為,闆級和晶圓級扇出型封裝都是封裝廠參與Chiplet的利器,全球最頂尖的幾家OSAT Chiplet技術開發工作都做得不錯。而且,目前晶片設計公司和封裝廠都在緊密配合大力發展Chiplet封裝。

長電科技也表示,公司在将近20年前已經開展了晶圓的封裝技術,海外的工廠也是當時最早和台積電一起對扇出型晶圓級封裝技術投入了巨資,進行了大量的專利和技術開發的工作。是以,确實這是産業未來發展的一個潮流。

不過,于大全也指出封裝廠做先進封裝的優勢不太明顯,因為越來越多的Chiplet是在有源晶片上做通孔或互聯,交由封裝廠來做會導緻風險過高。

總體而言,OSAT面臨前道企業在先進封裝技術領域的競争,必須尋求對應低成本高性能封裝技術,展開差異化競争,才能在激烈的競争中不斷發展。

大陸封裝業:在Chiplet上實作共赢

大陸地區的封裝行業已經在全球占據了非常重要的地位,在Chiplet的封裝方面表現如何呢?

“大陸Chiplet封裝技術相比業界頂級廠商還有差距,但不是很大。扇出型FOMCM和多晶片FCMCM已達到了較高水準,基于矽interposer和矽bridge(橋)的2.5D/3D技術也在發展中。”石磊表示。

需要注意的是,國際頂尖企業是在先進制程的基礎上進行Chiplet的封裝,大陸地區的晶圓制造尚在追趕先進工藝的路上。

“這也不代表我們沒機會,如果能在28nm平台上實作Chiplet也是件好事,就不需要14nm、7nm工藝了,但這也需要有相關企業來推動這件事情的發生。”于大全認為。

不過,對于UCIe聯盟的成立,廠商們還是給出正面的評價。長電科技表示,Chiplet還是需要形成一個事實上的标準化流程,以避免在市場規模還比較小的過程當中造成資源和技術的浪費,UCIe是一個非常好的方向。

石磊表示,“UCIe技術聯盟的成立時間還比較短,我們看到聯盟中也有OSAT,樂觀認為其能促進Chiplet生态圈的良性發展,能對OSAT封裝技術發展起到積極作用。”

集微網從采訪中也獲知,UCIe聯盟的成立是全球半導體行業的大事,大陸的産業鍊也正積極參與其中。長電科技表示,UCIe聯盟有逐漸公開參加成員的流程,大家後邊會看到包括長電科技在内,其他國内廠家都在積極地參與标準制定。并且,包括UCIe在内的幾個不同标準化制定工作也都有國内廠商所參與。

長電科技還希望業界對這個标準要保持耐心,“小晶片本身也還是剛剛起步,而标準化的工作是一個非常漫長的過程,我們要用發展的眼光來看待Chiplet相關的标準化工作。這種标準化應該由具有适當技術能力的 OSAT或封裝流程執行。”

石磊也指出,鑒于UCIe/Chiplets技術的複雜和難度,業界各環節的頂尖企業成立聯盟去讨論解決一些問題,是以各環節一定不要獨立盲目的去發展UCIe,應持有一個開放、包容和共赢的态度!”

最後,于大全認為整個Chiplet産業鍊都需要加強,“Chiplet實際上整合了很多技術,包括設計、制造、封裝等,是以整個産業鍊條都要往前發展,這樣才能最終實作自己的Chiplet。”(校對/Andrew)