處理器體系結構

一、前言

1、計算機系統隻限于機器語言程式級。

2、指令被編碼為有一個或多個位元組序列組成的二進制格式。一個處理器支援的指令和指令的位元組級編碼稱為它的指令集體系結構(ISA)。

3、雖然每個廠商制造的處理器性能和複雜性不斷提高,但是不同型号在ISA級别上都保持着相容。是以,ISA在編譯器編寫者和處理器設計人員之間提供了一個概念抽象層,編譯器編寫者隻需要知道允許哪些指令,以及他們是如何編碼的。而處理器設計者必須建造出執行這些指令的處理器。

4、現代處理器的實際工作方式可能跟ISA隐含的計算模型大相徑庭。ISA模型看上去應該是順序指令執行,也就是先取出一條指令,等到它執行完畢,再開始下一條。

5、在Web浏覽器或平衡二叉樹和哈希表這樣的資訊檢索資料結構中使用緩存,能夠在提高性能的同時,又保持一個更簡單、更抽象模型的功能。

6、HCL:一種描述硬體系統控制部分的簡單語言,可用于描述處理器設計。

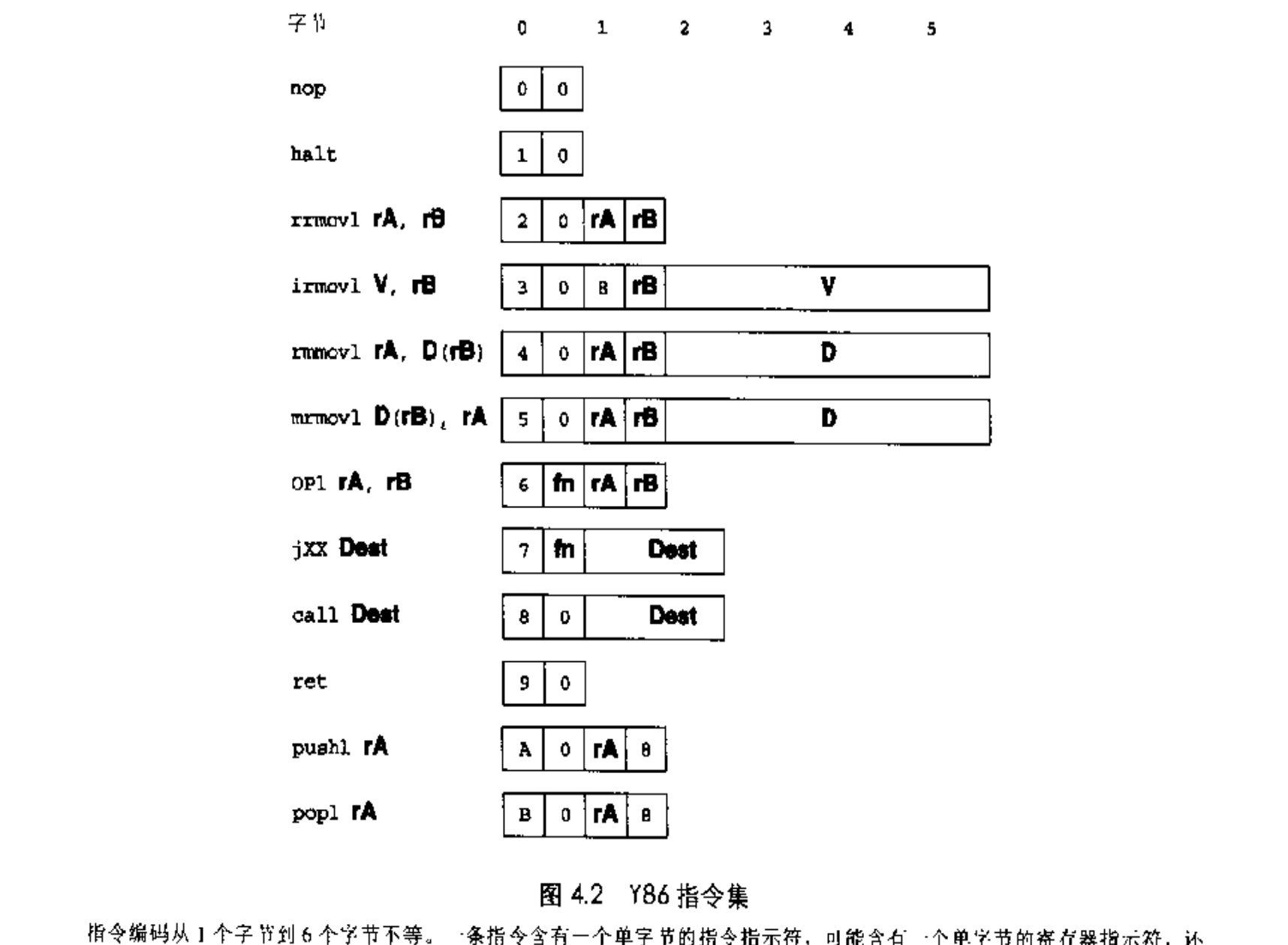

7、在本章中,我們定義一個簡單地不完備的指令集,稱之為“Y86”指令集。它基于順序操作、功能正确但有點不實用。由于處理器的每個時鐘周期執行一條完整地Y86指令,是以它的時鐘必須足夠慢,以允許在一個周期内完成所有動作。随後,我們建立一個流水線化的處理器,這個處理器将每條指令的執行分解成五步,每個步驟由一個獨立的硬體部分或階段來處理。指令步經流水線的各個階段,且每個時鐘周期有一條新指令進入流水線,是以處理器可以同時執行五條指令的不同階段。是以要求處理器能夠處理很多冒險或沖突。冒險就是一條指令的位置或操作數依賴于其他仍在流水線中的指令。

二、Y86指令集體系結構

定義一個指令集體系結構,包括定義各種狀态元素、指令集和他們的編碼、一組程式設計規範和異常事件處理。

1、程式員可見的狀态

程式員可見狀态:程式中的每條指令都會讀取或修改處理器狀态的某些部分。

Y86中包含:

①程式寄存器:%eax,%ecx,%edx,%ebx,%esi,%edi,%esp,%ebp。他們都可以存儲一個字。%esp被入棧、出棧、調用和傳回指令作為棧指針。

②PC(程式計數器):存放目前正在執行指令的位址。(在IA32中,用%eip表示,訓示将要執行的下一條指令在存儲器中的位址。)

③程式存儲器:就是一個很大的位元組數組,儲存着程式和資料。Y86用虛拟位址來引用存儲器位置,硬體和作業系統軟體聯合起來将虛拟位址翻譯成實際或實體位址,指明資料實際儲存在存儲器中哪個地方。

④條件碼:ZF、OF、SF。都是一位條件碼,用來儲存最近的算術或邏輯指令所造成影響的有關資訊。

⑤Stat:程式狀态的最後一個部分是狀态碼,它表明程式執行的總體狀态。它會訓示是正常運作還是出現了某種異常。

2、Y86指令

1)幾種指令

<<整數操作指令

addl 加

subl 減

andl 與

xorl 異或 并且它們隻對寄存器資料進行操作(差別于IA32,後者還允許對存儲器資料進行這些操作)。

<<條件碼

ZF-零

SF-符号

OF-溢出 <<跳轉指令——分支控制

jmp 直接跳轉

jle(SF^OF)|ZF 有符号數≤

jl SF^OF 有符号<

je ZF 相等/零

jne ~ZF 不相等/非零

jge ~(SF^OF) 有符号≥

jg ~(SF^OF)&~ZF 有符号> <<條件傳送指令

cmovle

cmovl

cmove

cmovne

cmovge

cmovg 2)指令解析

①在movl指令中,指令名字的第一個字母就表明了源類型。指令第二個字母指明了目的類型。立即數(i)、寄存器(r)、存儲器(m)。兩個存儲器傳送指令中的存儲器引用方式是簡單地基址和偏移量形式。在位址計算中,不支援第二變址寄存器和任何寄存器值的伸縮。不允許從一個存儲器位址直接傳送到另一個存儲器位址,也不允許将立即數傳送到存儲器。

②addl,subl,andl,xorl是四個整數操作指令,Y86中隻允許對寄存器資料進行操作(IA32中還允許對存儲器資料進行操作),這些指令會設定條件碼ZF、SF、OF。

③jmp,jle,jl,je,jne,jge,jg是七個跳轉指令,根據分支指令的類型和條件碼的設定來選擇分支。

④cmovle,cmovl,cmove,cmovne,cmovge,cmovg是六個條件傳送指令,這些指令的格式與寄存器-寄存器傳送指令rrmovl一樣,但隻有當條件碼滿足所需要的限制時,才會更新目的寄存器的值。

⑤call指令将傳回位址入棧,然後跳到目的位址。ret指令從這樣的過程調用中傳回。

⑥pushl和popl指令實作了入棧和出棧。

⑦halt指令停止指令的執行(IA32中的指令hlt)。IA32中應用程式不允許使用這條指令,因為它會導緻整個系統暫停運作。對于Y86而言,執行halt指令會導緻處理器停止,并将狀态碼設定為HLT。

3、指令編碼

①在上圖中還可看見指令的位元組級編碼。每條指令需要1-6個位元組不等。每條指令的第一個位元組表明指令的類型。這個位元組分為兩個部分,每部分4位:高4位是代碼部分,低4位是功能部分。功能值隻有在一組相關指令共用一個代碼時才有用。

②如圖,8個程式寄存器中每個都有相應0-7的寄存器标示符,Y86與IA32的寄存器編号一緻。程式寄存器存在CPU中的一個寄存器檔案中,這個寄存器檔案就是一個小的、以寄存器ID為位址的随機通路存儲器。當需要指明不應通路任何寄存器時,就用ID值0xF來表示。

③有的指令隻有一個位元組長,因為可能附加有寄存器訓示符位元組,指定一個或兩個寄存器。這些寄存器字段為rA,rB。有則有,無則無,隻有一個的則将第二個設為0xF。

④有的指令需要一個附加的4位元組常數字作為立即數資料或位址訓示符偏移量或分支指令和調用指令的目的位址。所有整數采用小端法編碼。

注意:分支指令和調用指令的目的位址是一個絕對位址,而不是像IA32中那樣使用PC相對尋址方式。處理器用PC相對尋址方式,分支指令的編碼會更簡潔,同時這樣也能允許代碼從存儲器的一部分複制到另一部分,而不需要更新所有的分支目标位址。

例如:

⑤指令集的一個重要性質就是位元組編碼必須有唯一的解釋。這個性質保證了處理器可以無二義性地執行目标代碼程式。即使代碼嵌入在程式的其他位元組中,隻要從序列的第一個位元組開始處理,我們仍然可以很容易地确定指令序列。反過來說,如果不知道一段代碼序列的起始位置,我們就不能準确地确定怎樣将序列劃分成單獨的指令。

4、Y86異常

程式員可見的狀态包括狀态碼Stat,它描述程式執行的總體狀态。代碼值如下:

①代碼值1:命名為AOK,表示程式執行正常,而其他一些代碼則表示發生了某種類型的異常。

②代碼值2:命名為HLT,表示處理器執行了一條halt指令。

③代碼值3:命名為ADR,表示處理器試圖從一個非法存儲器位址讀或者向一個非法存儲器位址寫,可能是當取指令的時候,也可能是當讀或者寫資料的時候。我們會限制最大的位址(确切的限定值因實作而異),任何通路超出這個限定值的位址都會印發ADR異常。

④代碼值4:命名為INS,表示遇到了非法的指令代碼。

遇到異常時,Y86會簡便處理使得處理器停止執行指令。在更完整地設計中,處理器會調用一個異常處理程式,這個過程被指定用來處理遇到的某種類型的異常。

5、Y86程式

Y86代碼與IA32代碼的主要差別在于,它可能需要多條指令來執行一條IA32指令所完成的功能。

Y86沒有伸縮尋址模式。

指令指明應該将代碼或資料放在什麼位置,以及如何對齊。這個程式詳細說明了棧的防治、資料初始化、程式初始化和程式結束等問題。

以“.”開頭的詞是彙編指令,他們告訴彙編器調整位址,以便在那兒産生代碼或插入一些資料。指令.pos0告訴編譯器應該從位址0處開始産生代碼。這個位址是所有Y86程式的起點。

建立Y86代碼的唯一工具是彙編器。

指令集模拟器YIS的目的是模拟Y86機器代碼程式的執行,而不用試圖去模拟任何具體處理器實作的行為。這種形式的模拟有助于在實際硬體可用之前調試程式,也有助于檢查模拟硬體或者在硬體上運作程式的結果。

6、一些Y86指令的詳情

大多數Y86指令是以一種直接的方式修改程式狀态的。

特指popl和pushl,在壓入/彈出棧指針%esp的時候,有兩種不同的約定:

1.壓入/彈出%esp的原始值

2.壓入/彈出%esp-/+4後的值 經過試驗,發現預設壓入彈出的都是原始值。

二、邏輯設計和硬體控制語言HCL

1.邏輯門:&&、|| 、!

2.組合電路:很多邏輯門組合成一個網,建構計算塊。建構這些網有兩條限制。

①兩個或多個邏輯門的輸出不連接配接在一起,否則可能會使線上的信号沖突,導緻一個不合法的電壓或電路故障

②網必須無環

3.字級的組合電路和HCL整數表達式:一些位級信号代表一個整數或一些控制模式。執行字級計算的組合電路根據輸入字的各個位,用邏輯門來計算輸出字的各個位。

- 所有字級的信号都聲明為int,不指定字的大小

- 多路複用函數用情況表達式來描述,具體格式如下:

[ select_1 : expr_1 select_2 : expr_2 …… ] - 從邏輯上講,這些選擇表達式是順序求值的。

- 選擇表達式為1時,表示如果前面沒有情況被選中,就選擇這種情況

- 不同 選擇表達式之間允許不互斥

4.多路複用器:根據輸入控制信号的值,從一組不同的資料信号則選出一個。多路複用函數是用情況表達式描述的。

5.算數/邏輯單元是很重要的組合電路,有三個輸入,标号為A、B的兩個資料輸入和一個控制輸入。根據控制輸入的設定,電路會對資料輸入執行不同的算數或邏輯操作。

6.判斷集合關系的通用格式

Iexpr in {iexpr1,iexpr2,…,iexprk} 7.兩類存儲器裝置

①時鐘寄存器(簡稱寄存器)存儲單個位或字,時鐘信号控制寄存器加載輸入值

②随機通路存儲器(簡稱存儲器)存儲多個字,用位址來選擇該讀或該寫哪個字 8.Y86處理器會用時鐘寄存器保持程式計數器(PC)、條件代碼(CC)、程式狀态(Stat)

9.寄存器檔案有兩個讀端口(A、B)還有一個寫端口(W),多端口随機通路存儲器允許同時進行多個讀和寫操作。

三、Y86的順序實作

1.将處理組織成階段

①取指:取指階段從存儲器讀取指令位元組,位址為程式計數器PC的值

②譯碼:譯碼階段從寄存器檔案讀入最多兩個操作數

③執行:在執行階段,算數/邏輯單元要麼根據ifun的值執行指令指明的操作,計算機存儲器引用的有效位址,要麼增加或減少棧指針

④訪存:訪存階段可以将資料寫入存儲器,或從存儲器讀出資料

⑤寫回:寫回階段最多可以寫兩個結果到寄存器檔案

⑥更新PC:将PC設定成下一條指令的位址

2.SEQ抽象視圖的畫法:

程式計數器放在寄存器中,位于左下角PC。

資訊随着線流動,方向是先向上再向右

回報先祖在右邊向下

所有硬體單元的處理都在一個時鐘周期内完成。

淺灰色方塊表示硬體單元

控制邏輯塊是用灰色圓角矩形表示的

線路的名字在白色橢圓中說明

寬度為字長或更窄的資料連接配接用細線

單個位的連接配接用虛線 3.部分指令執行步驟:

①執行rrmovl指令和執行算術運算類似,不過不需要取第二個寄存器操作數。将ALU的第二個輸入設為0,先把它和第一個操作數相加,得到valE=valA,然後再把這個值寫到寄存器檔案。

②對irmovl的處理與上類似,除了ALU的第一個輸入為常數值valC。因為是長指令格式,對于irmovl,程式計數器必須加6。所有這些指令都不改變條件碼

③pushl指令開始時很像前面講過的指令,但在譯碼階段,用%esp作為第二個寄存器操作數的辨別符,将棧指針指派為valB。在執行階段用ALU将棧指針減4,減過4的值就是存儲器寫的位址,在寫回階段還會存到%esp中。

④popl指令的執行與pushl的執行類似,除了在譯碼階段要讀兩次棧指針以外。popl應該首先讀存儲器,然後再增加棧指針。

⑤call指令、ret指令和pushl、pop類似。指令call:将call指令後面跟着的那條指令的位址valP壓入棧中,在更新PC階段将PC設為調用目的地valC。指令ret:在更新PC階段,将從棧中取出的值valM指派給PC。

⑥SEQ的實作包括組合邏輯和兩種存儲器裝置:時鐘寄存器、随機通路存儲器。

⑦需要對時序進行明确控制的四個硬體單元——程式計數器、條件碼寄存器、資料存儲器、寄存器檔案。

⑧計算原則:處理器從不需要為了完成一條指令的執行而去讀由該指令更新了的狀态。在時鐘上升開始下一個周期時,處理器就可以同時執行寄存器寫和存儲器寫。

具體通用步驟如下:

有些指令(整數運算)會設定條件碼,有些指令(跳轉指令)會讀取條件碼,但沒有指令必須既設定又讀取條件碼。雖然到時鐘上升開始下一個周期時才會設定條件碼,但是在任何指令試圖讀之前,它們都會更新。

4.常用常數

5.SEQ階段的實作

①取指階段:取指階段包括指令存儲器硬體單元。以PC作為第一個位元組(位元組0)的位址,這個單元一次從存儲器讀出6個位元組,第一個位元組被解釋稱指令位元組,分為兩個4位數。标号為“icode”和“ifun”的控制邏輯塊計算指令和功能碼等于從存儲器讀出值,或者當指令位址不合法時(imem_error指明),這些值對應于nop指令。

②譯碼和寫回階段:都要通路寄存器檔案。寄存器檔案有四個端口,支援同時進行兩個讀(端口A、B)和兩個寫(E、M),每個端口都有一個位址連接配接和一個資料連接配接。根據指令代碼icode以及寄存器訓示值rA和rB,可能還會根據執行階段計算出的Cnd條件信号。

③執行階段:執行階段包括算術/邏輯單元(ALU)第一步每條指令的ALU計算,執行階段還包括條件碼寄存器。

④訪存階段:訪存階段的任務是讀或者寫程式資料,兩個控制塊産生存儲器位址和存儲器輸入資料的值,另外兩個塊産生控制信号表明應該執行讀操作還是寫操作。當執行讀操作時資料存儲器産生值valM。

⑤更新PC階段:SEQ中最後一個階段會産生程式計數器的新值,依據指令的類型和是否要選擇分支,新的PC可能是valC、valM、valP

四、遇到的問題及解決方案

1、對于書上的一些流程示意圖有些看不懂,了解得有些困難。

2、SEQ的周期跟蹤,本來對于跳變原因有些不太了解。後來通過聯想,我想到了與大二學過的數字電路的上升沿觸發器的原理,發現這兩者有些相似,于是很快就了解了。

3、在做習題4.19時,發現自己的答案中比标準答案多了PC項,明明valM也有給PC值,後來看清了題目要求的是“目的寄存器”,而PC不屬于寄存器。

4、實驗樓操作時遇到的問題:

第一次進入實驗樓實驗環境時,我發現Code檔案夾中不存在shiyanlou_cs413檔案夾,于是我手動建立了一個。然後進入終端按照訓示一步一步執行指令,成功解析得出以下結果:

有同學反映他們的Code檔案夾内已經有shiyanlou_cs413檔案夾,并且執行第一條指令進入檔案夾以後出現(master)字樣,不能解析第二條指令位址。我本以為是我的電腦系統問題僥幸避開這個問題。但是後來由于操作失誤必須退出實驗樓重新再來,發現自己的執行中也出現了無法解析的問題。導緻後面操作無法繼續。跪求老師指教。

嘗試好多次以後發現還是不能解析。于是我嘗試在自己的虛拟機上做,可以解析。并且執行到了最後一步,雖然指令行中提示有一些錯誤但是還是像模像樣的。如圖:

但是依舊不知道為什麼之前不能。

解答:實驗樓支援git 後,課程目錄都會自動建立的,Code檔案夾中應該存在shiyanlou_cs413。

YIS編譯隻給了 make clean, make指令;我寫指導書發現沒有tcl tk的庫,我加了安裝庫的指令。

方法:apt-cache search tk; 查找相關的庫,然後sudo apt-get install 安裝。安裝完還不行,我又用ln -s 建立了快捷方式才可以。

現在的問題是 -lfl 的問題,可以推出缺少libfl.so, 這個是沒有flex安裝的問題 。

實驗樓普通使用者不能聯外網,是以不可以解析外部的網址,目前外網權限隻對會員開放了。

五、實驗實踐過程

要求:建構YIS環境:

cd ~/Code/shiyanlou_cs413

wget csapp.cs.cmu.edu/2e/sim.tar

tar -xvf sim.tar

cd sim

sudo apt-get install tk

sudo ln -s /usr/lib/x86_64-linux-gnu/libtk8.6.so /usr/lib/libtk.so

make

操作如下:

實驗樓中部分操作:

進入測試代碼,教材p239頁代碼為asuml.ys,可以通過。将代碼輸出在螢幕中,與書中一緻。

進行彙編,asuml.yo就是彙編後的結果:

六、參考文獻

1、《深入了解計算機系統》pdf

2、實驗樓實驗指導書:https://www.shiyanlou.com/courses/413 實驗五