資訊安全系統設計基礎第六周學習總結

第六周(10.12-10.18):

學習計時:共12小時

讀書:4

代碼:1

作業:3

部落格:4

第四章 處理器體系結構

現代微處理器可以稱得上是人類創造的最複雜的系統之一。一塊手指甲大小的矽片上,可以容納一個完整的高性能處理器、大的高速緩存,以及用來連接配接到外部裝置的邏輯電路。

2. 到目前為止,我們看到的計算機系統隻限于機器語言程式級。我們知道處理器必須執行系列指令,每條指令執行某個簡單操作,例如兩個數相加。指令被編碼為由一個或多個位元組序列組成的二進制格式。

3. 不同的處理器“家族”,例如intel ia32性能和複雜性不斷提高,但是不同的型号在ISA級别上都保持着相容。一些常見的處理器家族(例如IA32)中的處理器分别由多個廠商提供。

4. 1Y86指令集體系結構

4.1.1程式員可見的狀态

- Y86程式中的每條指令都會讀取或修改處理器狀态的某些部分。這稱為程式員可見狀态。這裡的“程式員”既可以是用彙編代碼寫程式的人,也可以是産生機器級代碼的編譯器。在處理器實作中,隻要我們保證機器級程式能夠通路程式員可見狀态,就不需要完全按照ISA隐含的方式來表示群組織這個處理器狀态。Y86的處理器狀态類似于IA32。

- 有8個程式寄存器:%eax、%ecx、%edx、%ebx、%esi、%edi、%esp和%ebp。處理器的每個程式寄存器存儲一個字。

- 程式計數器存放目前正在執行指令的位址。

4.1.2Y86指令

- Y86指令集基本上是IA32指令集的一個子集。它隻包括四位元組整數操作,尋址方式比較少,操作也較少。

- 四位元組資料,是以稱之為“字”不會有歧義。

- 彙編代碼格式類似于IA32的ATT格式。

4.1.3指令編碼

- 每條指令需要1~6個位元組不等,這取決于需要哪些字段。

-

Y86中的寄存器編号跟IA32中的相同。程式寄存器存在CPU中的一個寄存器檔案中,這個寄存器檔案就

是一個小的、以寄存器ID作為位址的随機通路存儲器。在指令編碼中以及在我們的硬體設計中,當需要指明不應通路任何寄存器時,就用ID值0xF來表示。

- 有的指令隻有一個位元組長,而有的需要操作數的指令編碼就更長一些。首先,可能有附加的寄存器訓示符位元組,指定一個或兩個寄存器。

- 從指令的彙編代碼表示中可以看到,根據指令類型,指令可以指定用于資料源和目的的寄存器,或是用于位址計算的基址寄存器。沒有寄存器操作數的指令,例如分支指令和call指令,就沒有寄存器訓示符位元組。那些隻需要一個寄存器操作數的指令将另一個寄存器訓示符設為OxF。這種約定在我們的處理器實作中非常有用。

- 有些指令需要一個附加的4位元組常數字。

4.1.4Y86異常

對于Y86,當遇到這些異常的時候,我們就簡單地讓處理器停止執行指令。在更完整的的設計中,處理器通常會調用一個異常處理程式,這個過程被指定用來處理遇到的某種類型的異常。就像在第8章中講述的,異常處理程式可以被配置成不同的結果,例如,放棄程式或者調用一個使用者自定義的信号處理程式。

4.1.5Y86程式

程式中以“.”開頭的詞是彙編器指令。

4.1.6一些Y86的詳情

- 大多數Y86指令是以一種直接的方式修改程式狀态的,是以定義每條指令想要達到的結果并不困難。不過,兩個特别的指令組合需要特别注意一下。pushl指令會把棧指針減4,并且将一個寄存器值寫入存儲器中。是以,當執行pushl %esp指令時,處理器的行為是不确定的,因為要入棧的寄存器會被同一條指令修改。

- 通常有兩種約定:1)壓入%esp的原始值,2)壓入減去4的%esp的值。

4. 2邏輯設計和硬體控制語言HCL

4.2.1邏輯門

4.2.2組合電路和HCL布爾表達式

圖4-11多路複用器根據輸入控制信号的值,從一組不同的資料信号中選出一個,在這個單個位的多路複用器中,兩個資料信号是輸入位a和b,控制信号是輸入位s,當s為1時,輸出等于a:而當s為0時,輸出等于b。在這個電路中,我們可以看出兩個AND門決定了是否将它們相對應的資料輸入傳送到OR門。

HCL表達式很清楚地表明了組合邏輯電路和C語言中邏輯表達式的對應之處。它們都是用布爾操作來對輸入進行計算的函數。值得注意的是,這兩種表達計算的方法之間有以下差別:

因為組合電路是由一系列的邏輯門組成,它的屬性是輸出會持續地響應輸入的變化。如果電路的輸入變化了,在一定的延時之後,輸出也會相應的變化。相比之下,C表達式隻會在程式執行過程中被遇到時才進行求值。

C的邏輯表達式允許參數是任意整數,0表示FALSE,其他任何值都表示TRUE。而邏輯門隻對位值0和1進行操作.

C的邏輯表達式有個屬性就是它們可能隻被部分求值。如果―個AND或OR操作的結果隻用對第一個參數求值就能确定,那麼就不會對第二個參數求值了。

4.2.3字級的組合電路和HCL整數表達式

- 通過将邏輯門組合成大的網,可以構造出能計算更加複雜函數的組合電路。通常,我們設計能對資料字進行操作的電路。有一些位級信号代表一個整數或一些控制模式。例如我們的處理器設計将包含有很多字,字的大小為4位和32位,代表整數、位址、指令代碼和寄存器辨別符。

- 執行字級計算的組合電路根據輸入字的各個位,用邏輯門來計算輸出字的各個位。

- 選擇表達式可以是任意的布爾表達式,可以有任意多的情況。這就使得情況表達式能描述帶複雜選擇标準的、多種輸入信号的塊。

4.2.4集合關系

在處理器設計中,很多時候都需要将一個信号與許多可能比對的信号做比較,以此來檢測正在處理的某個指令代碼是否屬于某一類指令代碼。

4.2.5存儲器和時鐘

為了産生時序電路,我們必須引入按位存儲資訊的裝置。儲存設備都是由同一個時鐘控制,時鐘是一個周期性信号,決定什麼時候要把新值加載到裝置中。考慮兩類存儲器裝置:

1.時鐘寄存器(簡稱寄存器)存儲單個位或字。時鐘信号控制寄存器加載輸入值。

2.随機通路存儲器(簡稱存儲器)存儲多個字,用位址來選擇該讀或該寫哪個字。随機通路存儲器的例子包括:1)處理器的虛拟存儲器系統,硬體和作業系統軟體結合起來使處理器可以在一個很大的位址空間内通路任意的字;2)寄存器檔案,在此,寄存器辨別符作為位址。在IA32或Y86處理器中,寄存器檔案有8個程式寄存器。

大多數時候,寄存器都保持在穩定狀态(用×表示)産生的輸出等于它的目前狀态。信号沿着寄存器前面的組合邏輯傳播這時,産生了一個新的寄存器輸入(用y表示)但隻要時鐘是低電位的,寄存器的輸出就仍然保持不變。當時鐘變成高電位的時候,輸入信号就加載到寄存器中,成為下一個狀态y直到下一個時鐘上升沿,這個狀态就一直是寄存器的新輸出。關鍵是寄存器是作為電路不同部分中的組合邏輯之間的屏障。每當每個時鐘到達上升沿時,值才會從寄存器的輸入傳送至輸出。

4.3 y86的順序(sequential)實作

4.3.1将處理組織成階段

通常,處理一條指令包括很多操作。将它們組織成某個特殊的階段序列,即使指令的動作差異很大,但所有的指令都遵循統一的序列。每一步的具體操作取決于正在執行的指令。建立這樣的架構,我們便能設計一個充分利用硬體的處理器。簡略描述:

取指

譯碼

執行

訪存

寫回

更新PC

我們面臨的一個挑戰是将每條不同指令所需要的計算放入到上述那個通用架構中。我們會使用圖4-17中所示的代碼來描述不同Y86指令的處理。表中的這種格式很容易映射到硬體,表中的每一行都描述了一個信号或存儲狀态的配置設定。閱讀時可以把它看成是從上至下的順序求值。當我們将這些計算映射到硬體時,會發現其實并不需要嚴格按照順序來執行這些求值。

4.3.2SEQ硬體結構

硬體單元與各個處理階段相關聯:

- 取指:将程式計數器寄存器作為位址,指令存儲器讀取指令的位元組。

- 譯碼:寄存器檔案有兩個讀端口A和B,從這兩個端口同時讀寄存器值

- 執行:執行階段會根據指令的類型,将算術/邏輯單元用于不同的目的。對整數操作,它要執行指令所指定的運算。對其他指令,它會作為一個加法器來計算增加或減少棧指針,或者計算有效位址,或者隻是簡單地加0,将一個輸入傳遞到輸出。

- 通路:在執行通路操作時,資料存儲器讀出或寫入一個存儲器字。

- 寫回:寄存器檔案有兩個寫端口。

4.3.3SEQ的時序

SEQ的實作包括組合邏輯和兩種存儲器裝置:時鐘寄存器,随機通路存儲器(寄存器檔案、指令存儲器和資料存儲器)。組合邏輯不需要任何時序或控制。對于較小的存儲器來說(例如寄存器檔案)這是一個合理的假設,而對于較大的電路來說,可以用特殊的時鐘電路來模拟這個效果。由于指令存儲器隻用來讀指令,是以我們可以将這個單元看成是組合邏輯。

4.3.4SEQ階段的實作

寄存器檔案有四個端口,它支援同時進行兩個讀(在端口A和B上)和兩個寫(在端口E和M)。每個端口都有一個位址連接配接和―個資料連接配接,位址連接配接是一個寄存器ID,而資料連接配接是一組32根線路,既可以作為寄存器檔案的輸出字,也可以作為它的輸入字。如果某個位址端口上的值為特殊辨別符0xF,則表明不需要通路寄存器。

4.4 流水線的通用原理

4.4.1計算流水線

在現代邏輯設計中,電路延遲以微微秒,也就是10的負12次方秒為機關來計算。

4.4.2流水線操作的詳細說明

為了更好地了解流水線是怎樣工作的,詳細看看流水線計算的時序和操作。圖4-34是三階段流水線的流水線圖,流水線階段之間的指令轉移是由時鐘信号來控制的"每隔120ps,信号從0上升至1開始下一組流水線階段的計算。

4.4.3流水線的局限性

4.4.4帶回報的流水線系統

4.5 y86的流水線實作

4.5.1SEQ+重新安排計算階段

作為實作流水線化設計的一個過渡步驟,我們必須稍微調整一下SEQ中五個階段的順序,使得更新PC階段在一個時鐘周期開始時執行,而不是結束時才執行。隻需要對整體硬體結構做最小的改動,對于流水線階段中的活動的時序,它能工作得更好。我們稱這和修改過的設計為“SEQ+”。我們移動PC階段,使得它的邏輯在時鐘周期開始時活動,使它計算目前指令的PC值。

4.5.2插入流水線寄存器

4.5.3對信号進行重新排列和标号

順序實作SEQ和SEQ+在一個時刻隻處理一條指令。在流水線化的設計中,與各個指令相關聯的值有多個版本,會随着指令一起流過系統。我們需要很小心以確定使用的是正确版本确版本的信号,否則會導緻很嚴重的錯誤。通過在信号名前面加上大寫的流水線寄存器名字作為字首,存儲在流水線寄存器中的信号可以唯一的被辨別。

4.5.4預測下一個PC

在PIPE―設計中,我們采取了一些措施來正确處理控制相關。流水線化設計的目的就是每個時鐘周期都發射一條新指令,也就是說每個時鐘周期都有一條新指令進入執行階段并最終完成。要是達到這個目的就意味着吞吐量是每個時鐘周期一條指令。要做到這一點,我們必須在取出目前指令之後,馬上确定下一條指令的位置。不幸的是,如果取出的指令是條件分支指令,要到幾個周期後,也就是指令通過執行階段之後,我們才能知道是否要選擇分支。類似地,如果取出的指令是ret,要到指令通過訪存階段,才能确定傳回位址。

4.5.5流水線冒險

PIPE-結構是建立一個流水線化的Y86處理器的好開端。不過,回憶4.44節中的讨論,将流水線技術引入一個帶回報的系統,當相鄰指令同存在相關時會導緻出現問題。在完成我們的設計之前,必須解決這個問題。

這些相關有兩種形式:

1)資料相關,下一條指令會用到這條指令計算出的結果;

2)控制相關,一條指令要确定下一條指令的位置,例如在執行跳轉、調用或傳回指令時,這些相關可能會導緻流水線産生計算錯誤,稱為冒險。同相關一樣,冒險也可以分為兩類:資料冒險和控制冒險。

4.5.6用暫停來避免資料冒險

暫停是避免冒險的―種常用技術,暫停時,處理器會停止流水線中一條或多條指令,直到冒險條件不再滿足,讓一條指令停頓在譯碼階段,直到産生它的源操作數的指令通過了寫回階段,這樣我們的處理器就能避免資料冒險,。它對流水線控制邏輯做了一些簡單的加強。當指令addl處于譯碼階段時,流水線控制邏輯發現執行、訪存或寫回階段中至少有―條指令會更新寄存器。

4.5.7用轉發來避免資料冒險

為了充分利用資料轉發技術,我們還可以将新計算出來的值從執行階段傳到譯碼階段,以避免程式prog4所需要的暫停。在周期4中,譯碼階段邏輯發現在訪存階段中有對寄存器%edX未進行的寫,而且執行階段中ALU正在計算的值稍後也會寫入寄存器%eaX。它可以将訪存階段中的值作為操作數Va1A也可以将ALU的輸出作為操作數~Va1B,注意,使用ALU的輸出不會導緻任何時序問題,譯碼階段隻要在時鐘周期結束之前産生信号Va1A和Va1B,在時鐘上升開始下一個周期時,流水線寄存器E就能裝載來自譯碼階段的值,而在此之前ALU的輸出已經是合法的了。

4.5.8加載/使用資料冒險

有類資料冒險不能單純用轉發來解決,因為存儲器在流水線發生的比較晚。

4.5.9異常處理

我們的指令集體系結構包括三種不同的内部産生的異常:1:)halt指令,2)有非法指令和功能碼組合的指令, 3)取指或資料讀寫試圖通路一個非法位址。正确處理異常是任何微處理器設計中很有挑戰性的一面。異常可能出現在不可預測的時間,需要明确的中斷通過處理器流水線的指令流。

4.5.10PIPE各階段的實作

4.5.11流水線控制邏輯

現在準備建立流水線控制邏輯,以完成我們的PIPE設計。這個邏輯必須處理以下4種控制情況,這些情況是其他機制(例如資料轉發和分支預測)不能能處理的:

處理ret:流水線必須暫停直到ret指令到達寫回階段。

加載/使用冒險:流水線必須暫停一個周期。

預測錯誤的分支:在分支邏輯發現不應該選擇分支之前,分支目标處的幾條指令已經進流水線了。必須從流水線中去掉這些指令。

異常:當―條指令導緻異常,我們想要禁止後面的指令更新程式員可見的狀态,并睏異常指令到達寫回階段時,停止執行。

我們先浏覽每種情況所期望的行為,然後再設計處理這些情況的控制邏輯。

4.5.12性能分析

我們可以看到,所有需要流水線控制邏輯進行特殊處理的條件,都會導緻流水線不能夠實作每個時鐘周期發射一條新指令的目标。我們可以通過确定往流水線中插入氣泡的頻率,來衡量這種效率的損失。因為插入氣泡會引發未使用的流水線周期。一條傳回指令會産生三個氣泡,一個加載/使用冒險會産生一個,而一個預測錯誤的分支會産生兩個。

4.5.13未完成的工作

- 多周期指令

- 與存儲系統的接口

4.6 小結

重點

- 第六周:學習任務教材 第四章

- 本章内容是處理器體系結構,重點掌握ISA,并能舉一反三;本章帶着大家設計并實作了一個結合CISC和RISC思想的處理器Y86,一個類IA32體系的處理器;ISA在編譯器編寫者和處理器設計者之間提供了一個抽象。

- 本章重點是4.1-4.3,流水線部分4.4-4.5供學有餘力的同學自學

- 練習題:4.1 4.2 4.5 4.6 4.8 4.10 4.11 4.12 4.16 4.17 4.19 4.21 4.24

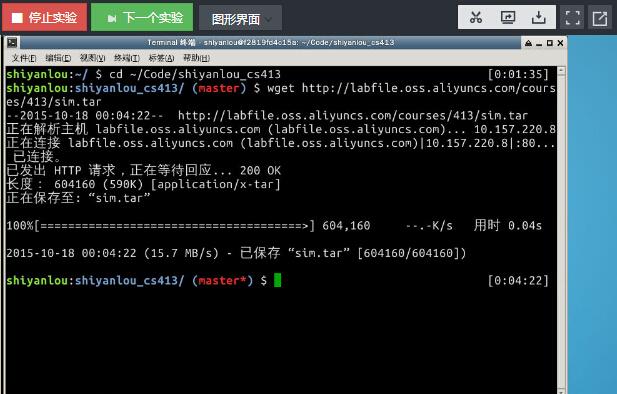

實驗樓實驗

過程

-

建構YIS環境:

cd ~/Code/shiyanlou_cs413

wget http://labfile.oss.aliyuncs.com/courses/413/sim.tar

tar -xvf sim.tar

cd sim

sudo apt-get install tk

sudo ln -s /usr/lib/x86_64-linux-gnu/libtk8.6.so /usr/lib/libtk.so

make

資訊安全系統設計基礎第六周學習總結 -

YIS測試:

cd y86-code

進入測試代碼,教材p239頁代碼為asuml.ys,可以通過

make asuml.yo

進行彙編,asuml.yo就是彙編後的結果,見教材p238。

make all

可以彙編運作所有代碼結果。

資訊安全系統設計基礎第六周學習總結

遇到的問題

在實驗樓中無法解析主機位址

還有不太清楚實驗樓中第一項任務的要求。

解決方法:在答疑論壇中看到了同學的提問和老師的回複。

實驗樓普通使用者不能聯外網,是以不可以解析外部的網址,目前外網權限隻對會員開放了。老師在實驗樓從業人員的幫助下,已經修改了實驗指導書,把外網位址改成内網位址了。

參考資料

- 教材:第四章《處理器體系結構》,詳細學習指導:http://group.cnblogs.com/topic/73069.html

- 課程資料:https://www.shiyanlou.com/courses/413 實驗五,課程邀請碼:W7FQKW4Y

- 教材中代碼運作、思考一下,讀代碼的學習方法:http://www.cnblogs.com/rocedu/p/4837092.html。

- 鼓勵自己好好讀書的連結,但說是入門級的書,可是我還是東西很多都看不懂:http://www.cnblogs.com/JeffreyZhao/archive/2009/11/23/recommended-reading-3-csapp.html

- 無意中翻到的一個程式員的故事:http://mindhacks.cn/2009/05/17/seven-years-in-nju/

感悟

- 遇到問題後我用過百度用各種方式查找實驗的問題,在不同的電腦上測試,果然還是答疑論壇最管用了。。。

- markdown真的很友善。

- 很多人說這本書是入門級教程,但是還是覺得不容易看懂。