第四章 處理器體系結構

第一節 Y86指令集體系結構

程式員可見的狀态

- 程式寄存器:%eax,%ecx,%edx,%ebx,%esi,%edi,%esp,%ebp。他們都可以存儲一個字。%esp被入棧、出棧、調用和傳回指令作為棧指針。

- PC(程式計數器):存放目前正在執行指令的位址。

- 程式存儲器:就是一個很大的位元組數組,儲存着程式和資料。Y86用虛拟位址來引用存儲器位置,硬體和作業系統軟體聯合起來将虛拟位址翻譯成實際或實體位址。

- 條件碼:ZF、OF、SF。都是一位條件碼,用來儲存最近的算術或邏輯指令所造成影響的有關資訊。

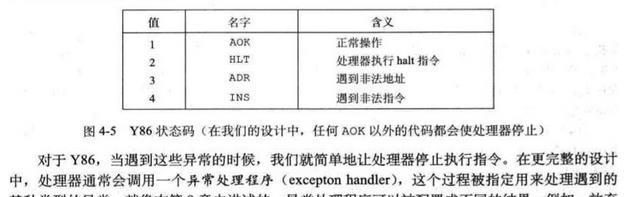

- Stat:程式狀态的最後一個部分是狀态碼,它表明程式執行的總體狀态。它會訓示是正常運作還是出現了某種異常。

Y86指令

1.在movl指令中,指令名字的第一個字母就表明了源類型。指令第二個字母指明了目的類型。立即數(i)、寄存器(r)、存儲器(m)。兩個存儲器傳送指令中的存儲器引用方式是簡單地基址和偏移量形式。

2.addl,subl,andl,xorl是四個整數操作指令,Y86中隻允許對寄存器資料進行操作。

3.jmp,jle,jl,je,jne,jge,jg是七個跳轉指令,根據分支指令的類型和條件碼的設定來選擇分支。

4.cmovle,cmovl,cmove,cmovne,cmovge,cmovg是六個條件傳送指令,這些指令的格式與寄存器-寄存器傳送指令rrmovl一樣,但隻有當條件碼滿足所需要的限制時,才會更新目的寄存器的值。

5.call指令将傳回位址入棧,然後跳到目的位址。

6.pushl和popl指令實作了入棧和出棧。

7.halt指令停止指令的執行(IA32中的指令hlt)。

指令編碼

每條指令的第一個位元組表明指令的功能

這個位元組分為兩個部分

高四位是代碼部分

低四位是功能部分

有的指令隻有一個位元組長,因為可能附加有寄存器訓示符位元組,指定一個或兩個寄存器。這些寄存器字段為rA,rB。有則有,無則無,隻有一個的則将第二個設為0xF。

有的指令需要一個附加的4位元組常數字作為立即數資料或位址訓示符偏移量或分支指令和調用指令的目的位址。所有整數采用小端法編碼。

Y86異常

Y86程式

- 以“.”開頭的詞是編輯器指令

- 指令 .pos0告訴編輯器應該從位址0處開始産生代碼,這個位址是所有Y86程式的起點

第二節 邏輯設計和硬體控制語言HCL

邏輯門

- 與(AND):Y=a&&b

- 或(OR):Y=a||b

- 非(NOT):Y=!a

組合電路和HCL布爾表達式。

兩個限制:

- 兩個或多個邏輯門的輸出不能連在一起

- 這個網必須是無環的

字級的組合電路和HCL整數表達式

在HCL中,多路複用函數是用情況表達式來描述的,格式如下:

[

select_1 : expr_1

select_2 : expr_2

...

select_k : expr_k

]

集合關系

判斷集合關系:

iexpr in {iexpr1,iexpr2,...,iexprk}

其中被測值iexpr和待比對的值iexpr1-iexprk

寄存器和時鐘

組合電路簡單的響應輸入信号,産生等于輸入的某個函數的輸出,并存在狀态在這個狀态上進行計時,如此産生了時序電路。

儲存器裝置:

- 時鐘計時器

-

随機通路儲存器

時鐘計時器:

随機通路儲存器:資訊安全系統設計基礎第六周學習總結 資訊安全系統設計基礎第六周學習總結

第三節 Y86的順序實作

将處理組織成階段

1.取指

2.譯碼

3.執行

4.通路

5.寫回

6.更新PC

SEQ硬體結構

4.訪存

SEQ的時序

四個硬體單元:

1.程式計數器

2.條件碼寄存器

3.資料存儲器

4.寄存器檔案

由于Y86指令集得本質,要遵循以下原則組織計算:

處理器從來不需要為了完成一條指令的執行而去讀由該指令更新了的狀态

SEQ階段的實作

- 取指階段,包括指令儲存器硬體單元

- 譯碼和回寫階段

- 執行階段,包括算數/邏輯單元

- 訪存階段,讀或寫程式資料

- 更新PC階段

- SEQ小結

第四節 流水線的通用原理

流水線化的一個重要特性是增加了系統的吞吐量

計算流水線

吞吐量={1 instruction/(加載寄存器時間+組合邏輯時間)}*{1000 picosecond/1 nanosecond}

流水線操作的局限性

書上的例子是一個理想的流水線化的系統,若将這個系統分成三個互相獨立的階段,每個階段所需的時間應是原來邏輯需要時間的三分之一,然而現實中不能實作。

原因:

1.不一緻的劃分

2.流水線過深,收益反而下降

作業

遇到的問題:

在建立環境時,已經建立了檔案,卻無法make。

參考來源:《深入了解計算機系統》