第四章 處理器體系結構

4.1 Y86指令集體系結構

4.1.1 程式員可見的狀态:Y86程式中的每條指令都會讀取或修改處理器狀态的某些部分。

8個程式寄存器:%eax、%ebx、%ecx、%edx、%esi、%edi、%esp、%ebp。存儲一個字。

存儲器:可以了解為很大的位元組數組,儲存着程式和資料。Y86用虛拟位址來引用存儲器位置。

實體位址:硬體和作業系統軟體聯合将虛拟位址翻譯成實際,指明資料實際儲存在存儲器的那個位置。

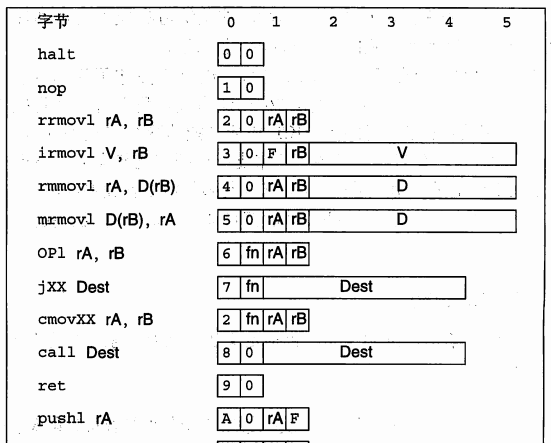

4.1.2 Y86指令:基本上是IA32指令集的一個子集。

Y86指令的更多細節

• mov指令分四個不同的指令,源可以是立即數i、寄存器r、存儲器m。目的可以是寄存器r、存儲器m。

存儲器傳送指令中的存儲器引用方式是簡單的基位址和偏移量形式。沒有mmmovl和immovl。

• 有4個整數操作指令,隻對寄存器資料進行操作。

• 7個跳轉指令。根據分支指令類型和條件碼的設定來選擇分支。

• 6個條件傳送指令。

• call指令傳回位址入棧,然後跳轉到目的位址。ret指令從這樣的調用過程中傳回

• pushl和popl實作入棧和出棧

• halt停止指令的執行。

4.1.3 指令編碼:寄存器标示符,寄存器訓示符位元組,4位元組常數字,相反。

确定位元組編碼的方法:

• 彙編碼表示的第一個位元組前端的位元組編碼

• 寄存器訓示符位元組

• 4位元組常數反序

重點掌握指令序列和位元組編碼的轉換。

4.1.4 Y86異常:異常處理程式

4.1.5 Y86程式

Y86和IA32的差別在于Y85可能需要多條指令來執行一條IA32指令所完成的功能。

彙編器指令:以“.”開頭的詞。告訴彙編器調整位址

4.1.6 Y86特别注意

pushl指令會把棧指針減4并将一個寄存器值寫入存儲器中。

4.2 邏輯設計和硬體控制語言HCL

4.2.1 邏輯門:AND &&. OR ||. NOT !

4.2.2 組合電路和HCL布爾表達式

限制:多個邏輯門的輸出不能連在一起;網必須是無的,即不能形成回路。

差別:電路的輸入變化會影響輸出的值;C的表達式參數允許是任意整數,邏輯門隻對位值0/1操作。

4.2.3 字級的組合電路和HCL整數表達式

字級計算的組合電路根據輸入字的各個位,用邏輯門計算輸出字的各個位。

不用指定字的大小。可以聲明位數。允許比較字是否相等。

情況表達式:

4.2.4 集合關系

判斷集合關系的通用格式:

4.2.5 存儲器和時鐘

• 時鐘寄存器:儲存單個位或字

• 随機通路存儲器:儲存多個字,用位址選擇該讀寫哪個字

4.3 Y86的順序實作

4.3.1 将處理組織成階段

各個階段(内)執行操作

取指:從存儲器中讀取操作,位址為程式計數器的值→譯碼→執行→訪存→寫回→更新PC

4.3.2 SED硬體結構

4.3.3 SED的時序

4.3.4 SED階段的實作

1、取指階段:包括指令存儲硬體單元,第一個位元組為指令位元組

2、譯碼和寫回階段:

寄存器檔案有四個端口,每個端口都有位址連結和資料連結

3、執行階段

4、訪存階段

5、更新PC階段

作業:

在上一個make時無法進入目錄,導緻後面沒法編譯