來自正點原子的學習筆記

我在學習的過程中會盡量把它和C語言進行比較,畢竟有較大的相似之處

Verilog程式架構

- 1 Verilog注釋

- 2 Verilog關鍵字

- 3 Verilog程式架構

-

- 3.1 基本内容介紹

- 3.2 子產品講解

- 3.3 主要部分的表達

- 3.4 完整的Verilog程式講解

- 3.5 子產品的調用(類似C語言的函數調用)

- 3.6 生成的原理圖

正文開始

1 Verilog注釋

同C語言,有兩種注釋方式

方式一:以//開頭,注釋到本行結束

code balabala // 這裡寫注釋!

方式二:以 結尾,中間都是注釋語句

code balabala

/*

這裡面都是注釋!

這也是!

*/

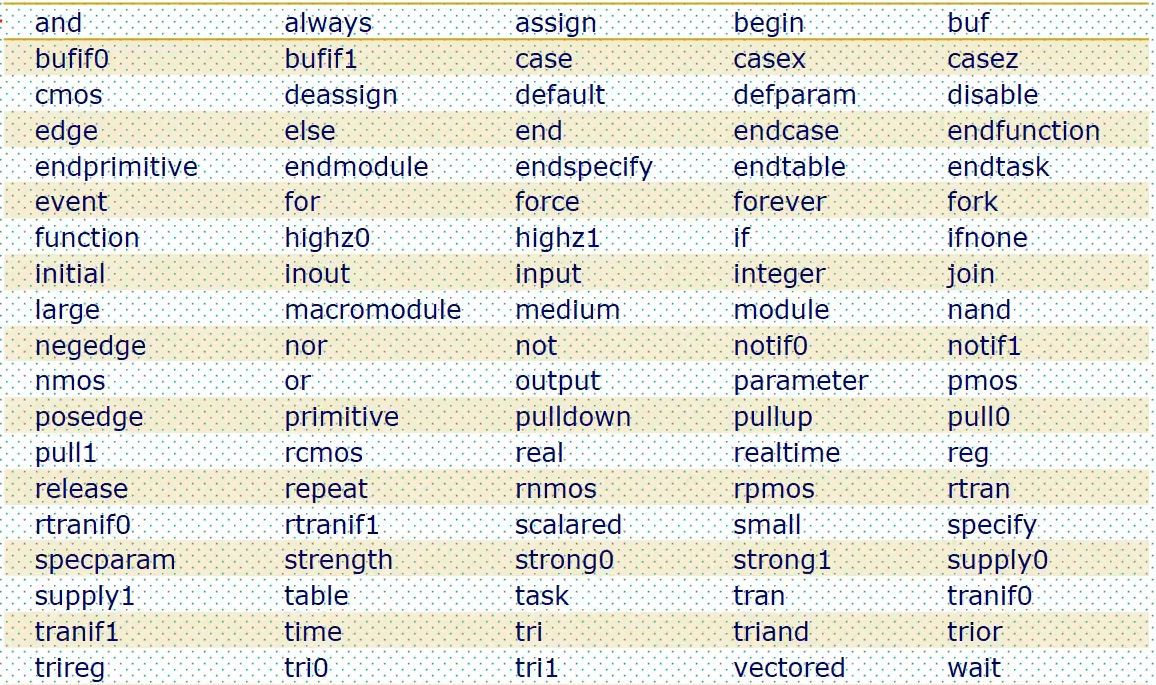

2 Verilog關鍵字

關鍵字是軟體/程式 會自動識别的一些詞

是以命名應該不與這一類重合,應避開

常用的關鍵字

3 Verilog程式架構

3.1 基本内容介紹

Verilog的基本設計單元是“子產品”(block)

類似于C語言的函數

一個子產品由兩部分組成,一部分描述接口,一部分描述邏輯功能

類似于C語言函數的參數和函數主體部分

每個Verilog程式包括四個主要部分:

端口定義、IO說明、内部信号聲明 (見程式)、功能定義

3.2 子產品講解

下面以一個子產品來講解

module 和endmodule分别表示子產品的開始和子產品的結束

(注意module一句結尾有分号!endmodule沒有!)

子產品名為block(建議命名直接一些)

接口是a,b,c,d(端口定義)

每一句完整的語句都和C語言需要一個 ;分号

input表示輸入,output表示輸出(IO說明)

assign 是給線網類型的變量指派的一種形式,abcd是wire類型的變量

c是a和b的或運算,d是a和b的與運算(這部分描述了整個子產品的功能)

不懂的可以回去看看哦,這是連結.

3.3 主要部分的表達

這是子產品的形象的圖形(端口定義和IO說明)

這是子產品的可綜合電路(功能定理部分)

可以這樣了解:可綜合的電路最終是能夠生成一個實體的電路的

而不可綜合的電路多用于仿真語句,此處就不贅述了。

3.4 完整的Verilog程式講解

流水燈程式結構

module flow_led(//子產品名稱

input sys_clk,//系統時鐘

input sys_rst_n,//系統複位,低電平有效

output reg [3:0] led //4個LED燈

//定義輸出端口是一個寄存器reg類型的端口,如果不指定,都是預設為wire線網類型的

);

//reg define

reg [23:0] counter ; //内部信号聲明

//*************************************************************************************

//* main code

//*************************************************************************************

//計數器對系統時鐘計數,計時0.2秒

always @(posedge sys_clk or negedge sys_rst_n)begin

if (!sys_rst_n)

counter <= 24'd0;

else fi (counter < 24'd1000_0000)

counter <= counter +1'b1;

else

counter <= 24'd0;

end

//通過移位寄存器控制IO口的高低電平,進而改變LED的顯示狀态

always @(posedge sys_clk or negedge sys_rst_n)begin

if (!sys_rst_n)

led <= 4'd0001;

else fi (counter < 24'd1000_0000)

led[3:0] <={led[2:0],;ed[3]};

else

led <= led;

end

endmodule//module和endmodule之間是程式的開頭和結尾

功能定義部分有三種方法:

1.assign語句 描述組合邏輯(見3.2)

2.always語句 描述組合/時序邏輯(本程式)

(具體兩者的差異,之後會講解)

3.例化執行個體元件 如:and#2 u1 (q,a,b);

and是關鍵字,與門。

上述三種邏輯功能是并行的,,,,,,,不同于C語言的串行!

注意:

在always塊中,邏輯是順序執行的。(内部)

而多個always塊之間是并行的。(外部)

3.5 子產品的調用(類似C語言的函數調用)

在子產品調用時,信号通過子產品端口在子產品之間傳遞。

eg:靜态數位管,這個子產品是一個Top上層子產品

例化的子產品是time_count部分,類似于C語言裡正在“調用函數”

其中還新起了一個名字,為u_time_count

這部分是端口的連接配接方式

左邊是這個子產品的端口,右邊是要連接配接的端口

進而實作底層子產品和上層子產品的信号互動

PS:flag是一個輸出信号,傳遞到頂層子產品的add_flag變量裡

下圖是這個子產品的定義,類似于C語言裡正在“定義函數”

紅色圈部分就是剛才提到的自身子產品的端口

另一種端口連接配接方式

與前一種端口連接配接方式不同(見紅色圈:左邊是輸出端口,右邊是傳入端口),

這種端口連接配接方式更加簡單

不過,需要更加嚴格的排列和一一對應

簡而言之,預設和省略了傳入信号的端口

(不推薦這種寫法)

還有一些細節

time _count #(

.MAX_NUM (TIME_SHOW)

這中.+參數名,是參數傳遞方法,後面是傳遞進的變量

3.6 生成的原理圖

注意之間的連接配接,之間的關系