Verilog實作二位十進制數字的顯示

文章目錄

- Verilog實作二位十進制數字的顯示

- 一、簡介

- 二、代碼

- 三、效果展示

一、簡介

我們這裡使用Verilog來實作二位十進制數字的顯示。

二、代碼

/*

這個是顯示數字的子產品,用了兩個數位管來顯示00-59的60個數字

*/

module number(seg_data_1,seg_data_2,seg_led_1,seg_led_2);

input [3:0] seg_data_1;

//數位管需要顯示0~9十個數字,是以最少需要4位輸入做譯碼

input [3:0] seg_data_2;

//小腳丫上第二個數位管

output [8:0] seg_led_1;

//在小腳丫上控制一個數位管需要9個信号 MSB~LSB=DIG、DP、G、F、E、D、C、B、A

output [8:0] seg_led_2;

//在小腳丫上第二個數位管的控制信号 MSB~LSB=DIG、DP、G、F、E、D、C、B、A

reg [8:0] seg [9:0];

//定義了一個reg型的數組變量,相當于一個10*9的存儲器,存儲器一共有10個數,每個數有9位寬

initial

//在過程塊中隻能給reg型變量指派,Verilog中有兩種過程塊always和initial

begin

seg[0] = 9'h3f;

//對存儲器中第一個數指派9'b00_0011_1111,相當于共陰極接地,DP點變低不亮,7段顯示數字 0

seg[1] = 9'h06;

//7段顯示數字 1

seg[2] = 9'h5b;

//7段顯示數字 2

seg[3] = 9'h4f;

//7段顯示數字 3

seg[4] = 9'h66;

//7段顯示數字 4

seg[5] = 9'h6d;

//7段顯示數字 5

seg[6] = 9'h7d;

//7段顯示數字 6

seg[7] = 9'h07;

//7段顯示數字 7

seg[8] = 9'h7f;

//7段顯示數字 8

seg[9] = 9'h6f;

//7段顯示數字 9

end

assign seg_led_1 = seg[seg_data_1];

assign seg_led_2 = seg[seg_data_2]; 之後編譯:

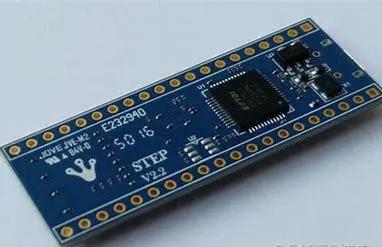

以及設定引腳:

然後進行燒錄:

三、效果展示

我們使用視訊來展示這個實驗的效果:

https://www.bilibili.com/video/BV1p44y1Y7t9?spm_id_from=333.999.0.0