第三課

Layout

power pin一般用M1、M2

power mesh/power grid一般用top meta(l高層金屬),是一種相對的概念,這裡的top metal概念與工藝檔案中的top metal不同

standard與power mesh所連接配接的pin也叫做follow pin

-

Custom Macro/Cell

模拟電路的版圖走線較為規則,用的是custom layout,講究power plan和floorplan

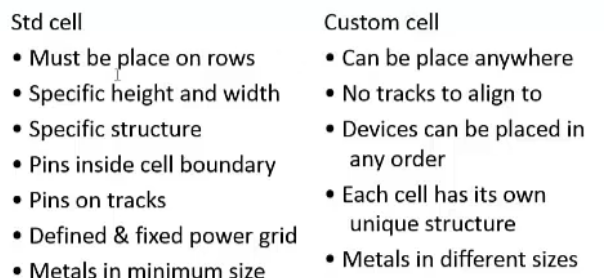

- Standard Cell vs. Custom 工藝中的6T、7T是track的意思

ICC布局布線 第三課

**晶片的面積分為die area和core area,full chip中式die area包括了core area,兩個框之間是boundry,中間填滿IO

**standard cell的走線routing大部分是壓着track走的,pin也基本上在track上,但并不絕對

**ICC的布局布線規則分為deault rule和non-default-rule(NDR),預設布線是以最窄線寬進行的,若要針對CLK等大負載信号線進行設定,則需要在ICC中用指令define_routing_fule改變線寬。

-

Silicon Layers & Metals

tap cell 就是半導體旁邊的n+區(以PNP管為例),用來連接配接襯底和電源,給襯底供電

氧化層分為栅氧和場氧,場氧用于隔離半導體

一般NWELL和PSUB的排列如上圖所示,tapcell會将NWELL連接配接至電源,PSUB接至地;DRC中要求每30u至少有一個tapcell,在power plan中放好。ICC布局布線 第三課

power mesh:越多越好

manufacture grid:與track不同,track是供icc走線的方格,實際流片時廠家還會要求版圖對齊manufacture grid

-

DFM

DFM會影響良率,包括double via(雙孔優化)的占比,widened wire和widen width的數值要求等等

-

Antenna affect

過長(或者說面積過大)的導線會吸引過多的電荷,擊穿栅氧化層

Floor Planning

-

Leaf cell

在ICC中輸入指令get_flat_cell可以擷取leaf cell,get_pin s-leaf可以擷取leaf cell的pin

leaf cell是指門級的單元,與hierarchy cell即層級單元不同

-

IO

有各種各樣的放法,包括:in_line和stagger,triple-stagger

電源IO擺放有規則要求,需要ESD保護,在電源IO中間擺放的信号IO個數也有要求

IO的結構:==IO上面分布有四個power,分别是VDDIO,VSSIO,VDDCORE和VSSCORE。==分别給IO power,IO ground,core mesh VDD以及core mesh VSS供電。

這四個接口是實體層面的接口,cell當中不會顯示(?),是以需要自己建立,手動連接配接。

-

Pad limited/Core limited

即晶片的面積是取決于pad還是core

Q&A

Q:有IO相關的資料嗎?

A:廠商會提供具體的spec文檔和布局要求檔案