圖形界面

打開icc圖形界面的指令:

icc_shell -gui

start_gui

gui_start

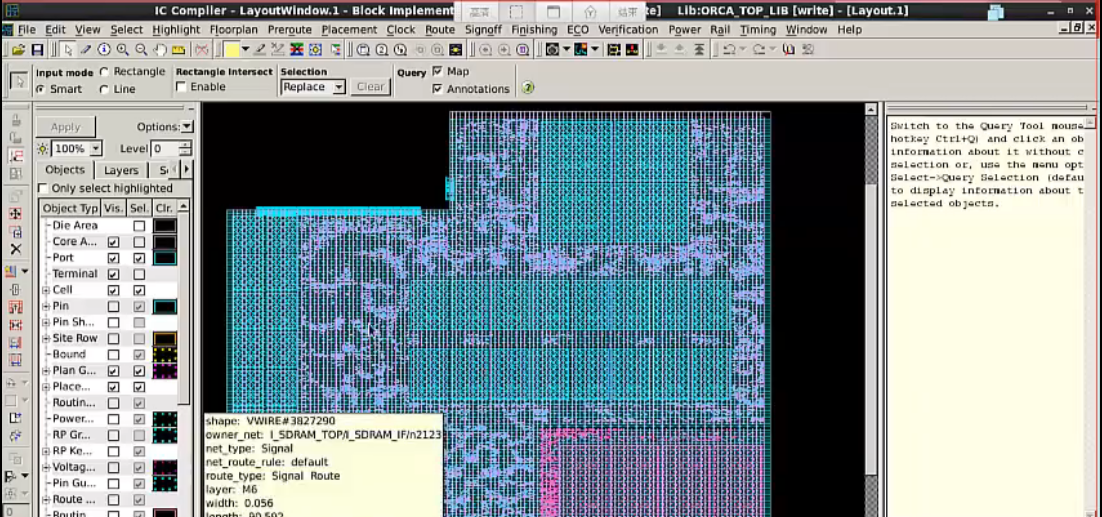

大緻的界面如下:

圖上是已經完成了布局布線的版圖,放大以後看可以看到标準單元都放在row上面

也有下圖所示無法看到内部結果的hardmacro

版圖顔色不同,表示power domain不同

在左邊的layer頁籤裡面可以選擇顯示的版圖層

軟體設定

第一步:

設定庫:

包括search_path,target_library以及link_library

設定完成後可以用echo或者puts檢查

-

target library和link library的差別

link library——library used for linking,verilog網表中的單元cell就是從link library中索引尋找的

target library——used for optimization,place_opt/cts_opt/route_opt等進行優化時,從target_library中索引尋找。

第二歩:

設定mlikway的參考庫:

set_mw_lib_reference ../work/ORCA_TOP_LIB #即馬上要建立milkway的目錄

-mw_reference_library "$MW_REFERENCE_LIB_DIRS $MW_SOFT_MACRO_LIBS" #在電路當中用到的基本單元的milkway

第三步:

建立milkway庫:

create_mw_lib -tech $TECH_FILE #工藝庫的.tf檔案

-bus_naming_style {[%d]}

-mw_reference_library $MW_REFERENCE_LIB_DIRS

注:出現以下的不比對warning是正常的

第四步:

打開milkway庫:

open_mw_lib $MW_DESIGN_LIBRARY

第五步:

讀入前端設計好的netlist /ddc檔案:

read_verilog -top $DESIGN_NAME $ICC_IN_VERILOG_NETLIST_FILE

輸入指令以後ICC會從之前設定的link library中尋找和設計中同名的基本單元,并進行連接配接。

視訊中用的是mcmm(multi-corner,multi-mode),載入的db庫比較多。

-

MCMM

corner:PVT

mode:func scan(shift/capture/speed)

一個corner和一個mode組合可以形成一個scenario(場景)

讀入設計以後ICC會預設進行link,用link -force指令可以強制重新連接配接,隻有當輸出為1時才可以進行後面的設定。

第六步:

進行後續的設定:

uniquify_fp_mw_cel #可以保證導入的設計中,每一個cell有獨有的命名

-

upf檔案

載入upf檔案:

load_upf $ICC_IN_UPF_FILE

在multi-power設計中,用于設定不同的power domain:

-

def檔案

如果晶片中含有DFT子產品,需要載入.scandef/.def檔案并設定相應的參數

**ORDERED類型的DFT單元不能被reordered,FLOATING則可以

.scandef檔案描寫了DFT鍊的連接配接方法,.def檔案則描述了晶片的形狀以及power和macro等的位置。

read_def

沒有載入def檔案時所有的單元都被放在左下的坐标點,沒有任何布局布線的資訊:

載入後布局如下所示:

輸出.def檔案可以用以下指令,用于儲存目前的布局資訊:

write_def -all_vias -output top.def

- scenario檔案

set cur_scenario [current_scenario]

set_active_scenarios

scenario檔案當中建構了不同場景:

每一個scenario都有對應的.sdc檔案

其它的相關操作:

gui界面想要喚出指令輸入界面,需按F7鍵,左邊的頁籤菜單用F8喚出。

選中單元以後按Q鍵可以打開屬性欄: