PlanAhead 與時序分析

在ISE 中可以進行時序分析,在PlanAhead 中同樣也可以進行時序分析。下面介紹用PlanAhead 進行時序分析的步驟。

一、 運作時序分析

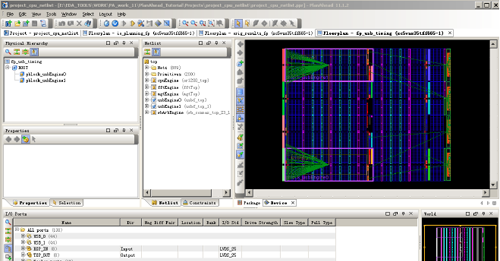

1. 在PlanAhead 中運作【File 】→ 【Open Project 】, 打開如下項目,PlanAhead_Tutorial/Projects/project_cpu_netlist/project_cpu_netlist.ppr , 會出現圖10-66 所示【Floorplan】視窗。

圖10-66 PlanAhead的Floorplan視圖

2. 選擇Floorplan – orig_results_fp頁籤。

3. 運作【Tools】→【Run TimeAhead】,打開圖10-67所示對話框,設定時序分析相關屬性。按圖中所示設定,單擊【OK】,開始時序分析。

圖10-67 時序分析屬性

4. 分析完成,時序分析結果如圖10-68所示。圖中顯示了時序的類型、裕量、源/目的對象、總延時、邏輯延時、網線延時百分比以及邏輯級數。

圖10-68 時序分析結果【Timing Results】

圖中紅色為時序違例的路徑,需要設計者檢查并修正。

5. 選擇Path1路徑,并最大化【Properties】視窗,如圖10-69所示,可以看到此路徑的詳細資訊,包括源時鐘路徑、目的時鐘路徑和資料路徑等,其中詳細列出了每條路徑的組成及元件延時和網線延時資訊。

圖10-69 時序路徑屬性

二、 在【Schematic】視圖中探測時序路徑。

1. 顯示原理圖結構1。

在【Timing Results】視窗的Path1路徑右鍵彈出菜單中選擇【Schematic】,打開如圖10-70所示原理圖結構視圖。

2. 顯示原理圖結構2。

在【Timing Results】視窗的【From】列選擇所有以usbEngine0/…打頭的路徑,單擊滑鼠右鍵,在彈出菜單中選擇【Schematic】,打開圖10-71所示多個時序路徑原理圖視圖。

3. 顯示層次結構。

在圖10-71【Schematic】視窗的右鍵菜單中選擇【Select Primitive Parents】,再次在右鍵菜單中選擇【Show Hierarchy】,則包含【Schematic】視窗中所示的兩個部分邏輯的設計子產品會顯示在【Hierarchy】視窗中。如圖10-72所示。

圖10-70 時序路徑原理圖視圖

圖10-71 多個時序路徑原理圖視圖

圖10-72 層次視圖

三、 編輯時序限制

1. 将TS_cpuClk周期限制由11.75ns改為11.5ns。

在圖10-73中,選擇【Netlist】頁籤旁邊的【Constraits】頁籤,選擇圖中所示TS_cpuClk限制,在【Constraint Properties】屬性視窗可以看到此限制的相關屬性,在這裡可以編輯限制名、周期、占空比、分組以及優先級。這裡隻需将11.75ns更改為11.5ns,這時會在【Constraint Properties】屬性視窗出現一個【Apply】按鈕,單擊就可以完成限制修改。

圖10-73 修改時序限制

2. 建立時序限制。

在圖10-74中【Constraint】視窗單擊

,彈出【Create New Timing Constraint】對話框,可以選擇一個限制類型,并添加新的時序限制。

圖10-74 建立時序限制