在Quartus II里仿真Verlog设计

本文介绍Quartus II仿真器的基本特点。演示仿真器如何判断电路的正确性和性能。

目录

l 范例电路

l 使用波形编辑器

l 功能仿真

l 时序仿真

Quartus II软件包含一个仿真器(当然是10.0之前的版本才有J),可用来对在Altera的可编程器件里实现的设计电路做行为和性能仿真。使用测试变量作为输入,观察生成的响应。另外,为了观测I/O引脚的仿真值,可在电路的内部节点添加探针。仿真器使用波形编辑器,便于表达期望的信号。

本文的目标:

l 测试设计电路所需的测试变量

l 使用Quartus II波形编辑器画测试波形

l 功能仿真,验证综合的电路的功能正确否

l 时序仿真,考虑延迟

先决条件

安装Quartus II软件。本文使用9.1版本,其他版本或稍有不同。

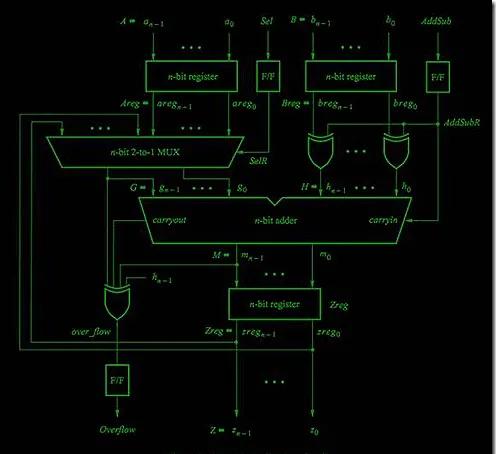

1 范例电路

范例使用图1所示的adder/subtractor电路。电路执行加、减运算,并以2的补码形式将n-bit数字累加。2个主要的输入是数字A和B,主要的输出是Z。其他的输入有加减控制信号AddSub,当AddSub=0时,Z=A+B;当AddSub=1时,Z=A-B。另一个输入信号Sel,用来控制累加操作的模式。当Sel=0时,Z=A+-B;当Sel=1时,B加到或从Z中减去。如果加减操作有算术溢出,用输出信号Overflow表示。

为了便于处理异步输入信号,在时钟上升沿将他们加载到触发器。因此,输入A和B加载到寄存器Areg和Breg,而Sel和AddSub各自加载到触发器SelR和AddSubR。电路将结果放到寄存器Zreg。

下面,我们用Verilog代码实现一个16位的加减器电路:

l 创建一个工程addersubtractor.

l 添加addersubtractor.v文件添加到工程,这个文件可在DE2光盘的DE2——tutorials\design_files目录找到。

l 选择目标芯片Cyclone II EP2C35F672C6.

l 编译。

代码:

View Code

1 //Top-level module

2 module addersubtractor(A,B,Clock,Reset,Sel,AddSub,Z,Overflow);

3 parameter n=16;

4 input [n-1:0]A,B;

5 input Clock,Reset,Sel,AddSub;

6 output [n-1:0]Z;

7 output Overflow;

8 reg SelR,AddSubR,Overflow;

9 reg [n-1:0]Areg,Breg,Zreg;

10 wire [n-1:0]G,H,M,Z;

11 wire carryout,over_flow;

12

13 //Define combinational logic circuit

14 assign H=Breg^{n{AddSubR}};

15 mux2to1 multiplexer(Areg,Z,SelR,G);

16 defparam multiplexer.k=n;

17 adderk nbit_adder(AddSubR,G,H,M,carryout);

18 defparam nbit_adder.k=n;

19 assign over_flow=carryout^G[n-1]^H[n-1]^M[n-1];

20 assign Z=Zreg;

21

22 //Define flip-flop and registers

23 always @(posedge Reset or posedge Clock)

24 if(Reset==1)

25 begin

26 Areg<=0;

27 Breg<=0;

28 Zreg<=0;

29 SelR<=0;

30 AddSubR<=0;

31 Overflow<=0;

32 end

33 else

34 begin

35 Areg<=A;

36 Breg<=B;

37 Zreg<=M;

38 SelR<=Sel;

39 AddSubR<=AddSub;

40 Overflow<=over_flow;

41 end

42 endmodule

43

44 //k-bit 2-to-1 multiplexer

45 module mux2to1(V,W,Selm,F);

46 parameter k=8;

47 input [k-1:0]V,W;

48 input Selm;

49 output [k-1:0]F;

50 reg [k-1:0]F;

51

52 always @(V or W or Selm)

53 if(Selm==0)

54 F=V;

55 else

56 F=W;

57 endmodule

58

59 //k-bit adder

60 module adderk(carryin,X,Y,S,carryout);

61 parameter k=8;

62 input [k-1:0]X,Y;

63 input carryin;

64 output [k-1:0]S;

65 output carryout;

66 reg [k-1:0]S;

67 reg carryout;

68

69 always @(X or Y or carryin)

70 {carryout,S}=X+Y+carryin;

71 endmodule

72 2 使用波形编辑器

在仿真之前,要创建一个期望的波形,表示输入信号。也需要指定设计者希望观测的输出信号和电路的内部节点。画波形的方法如下:

1. 打开波形编辑器,File / New,在图3所示的窗口选择Vector Waveform File并单击OK。

图 3

2. 波形编辑窗口如图4所示。以addersubtractor.vwf保存波形文件。注意窗口标题栏的文件名称也随之改变。设置仿真时间为180ns:Edit / End Time / 输入180ns。选择View / Fit in window显示全部仿真时间窗口。

图 4

3. 接下来,添加输入/出信号。单击Edit / Insert Node or Bus打开图6所示的窗口。单击Node Finder打开窗口7.因为要添加输入/出引脚,将filter设为Pins:all。单击List。选定要添加的信号:Clock,Reset,Sel,AddSub,A,B,Z,Overflow。OK。

图 6

图 7

图 8

4. 指定输入信号的逻辑值。输出信号Z和Overflow的值由仿真器自动生成。变量的值设置如图9所示。

使用Overwrite Clock图标

将时钟周期设为20ns。依次设置其他输入信号,设置完毕,如图11所示。

图 10

图 11

5. 为了便于查看,将A,B,Z以有符号的10进制的形式显示。如图12.用Arbitrary Value图标

指定A,B的值,如图13。保存。

图 12

图 13

3. 执行仿真

仿真分为功能仿真和时序仿真。通常,功能仿真用于验证电路的功能是否正确。

3.1 功能仿真

要执行功能仿真,选择Assignment / Settings打开图14所示的设置窗口。指定仿真类型为Functional。在仿真之前,要创建网表,选择Processing / Genereate Functional Simulation Netlist。

选择Processing / Start Simulation或者单击图标

开始仿真。仿真结束,结果如图15.注意最后一个Z值错误,因为算术溢出,所以对应的Overflow为1.

图 14

图 15

上面只仿真了输出信号,同样可以添加电路内部信号,比如寄存器信号,来仿真。只需在添加信号的地方将filter改为Registers: post-fitting即可添加。

3.2 时序仿真

经过功能仿真验证后,可时序仿真查看电路的速度如何。将仿真模式改为Timing。仿真结果如图16.