本節書摘來自華章出版社《cmos內建電路後端設計與實戰》一 書中的第3章,第3.2節,作者:劉峰,更多章節内容可以通路雲栖社群“華章計算機”公衆号檢視。

目前,标準單元庫的設計面臨着新的挑戰。首先,由于晶片內建度越來越大,功耗成為設計中需要着重考慮的因素之一;其次,從成本考慮,晶片的面積使用率需要進一步優化;其三,由于系統級晶片的工作頻率越來越高,進而對晶片的工作性能提出了更高的要求。目前,許多eda廠商推出了針對深亞微米技術帶來的問題解決方案與工具,但從現有的設計流程來說,對标準單元庫進行針對深亞微米技術的優化仍是最關鍵的步驟。然而出于成本的考慮,通常在标準單元庫中很難同時綜合考慮高速、低功耗、面積來進行優化。

內建電路設計中的單元庫是所需單元符号庫、單元電路結構庫、版圖庫、電路性能參數庫、功能描述庫、設計規則和器件模型參數庫的總稱。從系統行為描述、邏輯綜合、邏輯功能模拟,到時序分析、驗證,直至實體設計中的自動布局、布線,都必須有一個内容豐富、功能完整的單元庫的支援。另一方面,在自底向上的設計流程中,設計是從單元庫中一個個具體單元開始的,逐漸構成各級功能子產品,直至整個系統。

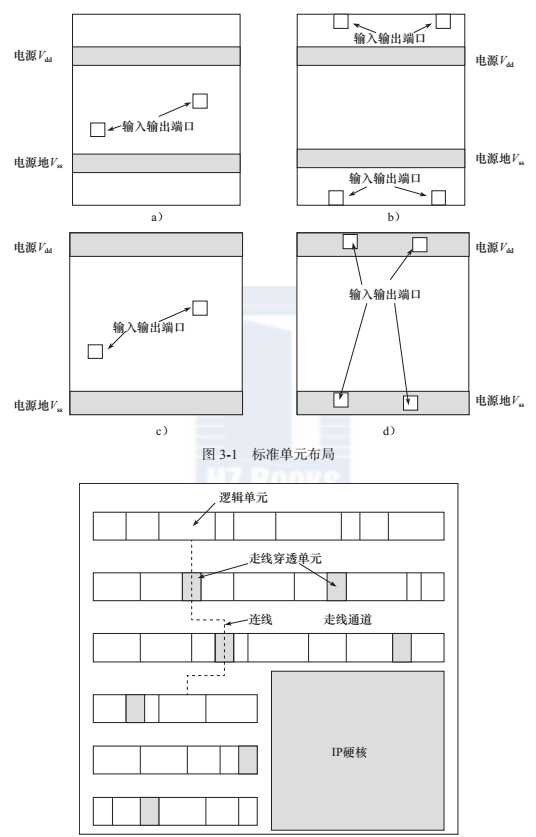

标準單元法是庫單元設計方法的一種,标準單元法的特點是各個單元高度相同寬度不等,單元寬度随單元功能的複雜程度而變,所有單元的電源線和地線位置相同,如圖3-1所示。

圖3-1所示為4種不同的電源線和地線的實作形式,可以看出電源線和地線可以處在單元的任何位置,目前主流的設計是選取圖3-1c的實作形式,電源線和地線處在單元的最上端和最下端,信号端口處于單元的内部區域。在用标準單元構成電路版圖時,每行單元的電源線、地線自然拼接。

标準單元庫是用全定制方法精心設計好各種單元電路的版圖,然後把這些經過優化設計并驗證通過的單元版圖存入資料庫。晶片設計中根據設計需要調用單元庫中的單元并将其排列成若幹行,然後根據邏輯網表的連接配接要求将各單元的端口用金屬線連接配接起來,最終得到所要求的晶片版圖。

由于單元庫中各個單元的高度相等、寬度不限,單元中的電源、地線及輸入輸出端口位置都有特殊的規定,使得單元與單元連接配接變得簡單、有條理,布局也有規律,為以後的高層次的系統設計帶來了很大的友善,使得本來很複雜、工作量很大的系統實體實作變得相對簡單、容易,并且帶有很強的規律性。

早期基于标準單元的實體實作,由于有限的布線資源,需要專門留有布線通道,如圖3-2所示。

現在由于工藝越來越先進,在器件尺寸不斷縮小的同時,提供布線資源的金屬層數也逐漸增多,單元與單元之間的連接配接可以直接通過不同層金屬進行連接配接,是以一般情況下,已經不再需要布線通道的存在了,如圖3-3所示。

标準單元庫中至少要包括and(與)門、or(或)門、not(非)門、dff時序單元,這幾類單元可以實作大部分的基本邏輯功能。除了這幾類最基本的單元,對于晶片的實作還需要tie-high、tie-low、f?iller等實體實作所需的非邏輯功能單元,比如填充單元(f?iller)是在标準單元布局完成以後,用來把所有标準單元的電源和地以及構成半導體的阱都連起來的實體輔助單元。

随着內建電路制造技術技術的迅速發展和系統級晶片(soc)的規模越來越大,設計越來越複雜。采用全定制設計提高了設計的性能和實體密度,但是成本太高。基于單元的設計優點是對于一個給定的工藝,單元隻需要設計和驗證一次,然後就可以重複利用多次,是以分攤了設計成本。為了縮短設計過程并使設計自動化,基于單元的設計越來越受青睐。标準單元庫在基于單元的設計中地位十分重要,它是設計的基礎,它為基于單元的設計流程的各個階段提供支援,對設計的性能、功耗、面積和成品率至關重要。

一般來說各種門電路、觸發器及各種i/o單元是一個标準單元庫所必需的配置,這些配置可以滿足一個純數字電路的設計需要。其他大型複雜宏單元,例如模拟單元、記憶體(rom、ram、sram)單元等,在許多流片廠商中往往是作為ip形式提供的,是以也可以不完全納入标準單元庫中。标準單元分類簡圖如圖3-4所示。

通常标準單元庫中的标準單元按功能分類一般分為以下幾種:

1)邏輯門單元。邏輯門單元是指具有邏輯功能的單元,比如與門、或門、與非門、或非門、與或非門、或與非門、異或門等,并且每種類型的邏輯門存在多個不同驅動強度的單元。

2)驅動單元。驅動單元分為邏輯正向和邏輯反向兩種形式,通常邏輯正向驅動單元稱作緩沖器(buffer),邏輯反向驅動單元稱作反相器(inverter)。每種驅動單元可以提供多個不同輸出驅動能力的單元。

3)時序單元。時序單元指用于儲存邏輯狀态的單元,比如觸發器、鎖存器、移位寄存器等。其中觸發器又包括d觸發器、rs觸發器、jk觸發器和t觸發器,每種觸發器還可以設有清零/置位端等。

4)運算單元。運算單元包括半加器、全加器、減法器和二位比較器等。這些單元通過級聯的方式可構成更多位的運算單元如乘法器、除法器等。

5)混合邏輯單元。混合邏輯單元具有比較複雜的邏輯功能,比如多路選擇器、計數器、編碼器、譯碼器、奇偶發生器等。

6)i/o單元。i/o單元是晶片與外界交換資訊的接口單元,其接口端用于輸入輸出的金屬壓焊塊(pad)。

7)實體單元。實體單元指沒有邏輯功能但是在實體實作上需要使用的單元,比如tie-high、tie-low、f?iller單元等。

有的進階标準單元庫中還設計了如時序單元陣列、乘加部件等功能比較複雜的宏單元,為滿足使用者的特殊要求而加入的擴充單元。

一個好的标準單元庫應該能提供綜合工具實作各種可靈活選擇的單元,這樣能夠為設計提供最優的邏輯實作結果。是以良好的标準單元庫應該具備如下幾個特點:

1)擁有各種邏輯單元類型并且同時提供多種驅動力強度的同類型單元。

2)緩沖器(buffer)和反相器(inverter)的驅動強度變化範圍大。

3)擁有上升和下降時間均衡的驅動單元,該類型單元主要用于時鐘樹的實作中。

4)擁有相同邏輯功能,但輸出可以同時提供正向和反相輸出的時序單元,比如時序單元的輸出即有正向輸出q端也有輸出取反端qn。

5)擁有相同的邏輯功能,但分别提供輸出正向和輸出反相的組合邏輯單元,比如與門單元(and)和與非門單元(nand)。

6)擁有多種高扇入的邏輯單元,用于邏輯優化,比如多輸入或與非門單元(oai)。

7)擁有多種驅動強度的正沿觸發和負沿觸發的時序單元。

8)擁有多種不同置位複位端組合的時序單元。

9)擁有多種用于修正保持時間違反的延時單元。

10)擁有各種靈活的實體單元,用于實作複雜晶片版圖的完整性。

标準單元庫支援設計所需的标準單元庫模型的資料主要包括:

1)gdsii版圖庫。gdsii版圖含各種标準單元的實體版圖(全部掩膜版資料),一般采用全定制圖形編輯方式進行設計。gdsii版圖也是标準單元庫的核心部分,這些版圖庫可以用來生成自動布局、自動布線後的電路版圖,并可以對版圖進行工藝規則的檢查、電特性規則檢查、版圖參數提取以及版圖和原理圖的互相校驗。如果是更複雜的版圖還可以用細緻的eda驗證工具進行驗證。

2)符号庫。符号庫用于電路的邏輯輸入,是用幾何圖形表示單元的符号。符号庫用于定義和命名單元的輸入/輸出引線,每一個單元都有表示該單元的邏輯符号和輸入/輸出引線的名稱。

3)lib時序庫。lib時序庫用于描述每個标準單元的基本邏輯功能、延遲時間參數等,其中延遲時間參數是通過投片測試或仿真提取獲得的。每一個标準單元中都列出了該單元的功能、真值表和有關的延遲參數,利用這些單元的功能參數庫可以進行電路的verilog/vhdl數字仿真,确定所設計電路的功能正确與否,檢查異步時序電路中的競争和冒險等工作。

4)lef布局布線庫。lef布局布線庫用于描述每一個标準單元版圖的外形尺寸、輸入輸出端口的幾何位置坐标和圖形特征等,用于标準單元實作方法中的自動布局、布線調用。利用lef布局布線庫,就可不必考慮太多單元版圖内部的細節來布局布線,進而大大地減少了布局布線工具對實體版圖資料的處理量。

5)spice網表。spice網表是标準單元的電路網表,主要用于做版圖與電路圖一緻性檢查即實體驗證中的lvs檢查。

6)verilog與vhdl仿真模型。verilog與vhdl仿真模型主要用于前端設計時,做代碼綜合和功能仿真驗證。

對于标準單元庫,設計者總是非常關心單元的一些重要參數,比如單元延遲參數、扇出延遲特性、線延遲參數、最高工作頻率等,因為隻有清楚地知道這些單元參數及特性之後,在利用這些庫進行設計時才能把握設計靈活性使設計結果最優化。在內建電路代工廠生産工藝特征尺寸不斷縮小的同時,晶片的邏輯參數(時延、功耗、建立時間、保持時間等)也必須随工藝的不斷進步而不斷更新。

标準單元在實體版圖上所遵循的主要參數資訊如圖3-5所示。

1)門栅長度(drawn gate length)。該參數用于說明該标準單元的栅長度,一般是指工藝大小,比如0.13μm、0.028μm。

2)金屬層數(layers of metal)。該參數用于說明标準單元庫所在的工藝下,能使用的金屬層數。

3)版圖格點(layout grid)。該參數用于說明标準單元版圖可編輯的最小間距,比如0.005μm。

4)垂直pin腳格點(vertical pin grid)。該參數用于說明垂直走線方向上pin腳的格點間距是多少。在标準單元設計方法中,大多數的布局布線工具能夠對位于格點上的pin腳進行高效地端口連接配接,是以所有标準單元的pin腳應該位于垂直和水準格點上,關于格點的概念會在後面章節中說明。

5)水準pin腳格點(horizontal pin grid)。該參數用于說明水準走線方向上pin腳的格點間距是多少。

6)單元電源和地線寬帶(cell power and ground rail width)。該參數用于說明标準單元所用電源地線的寬度。

7)單元高度(cell height)。該參數用于說明标準單元的高度,主要說明該高度能包含多少水準方向上的布線通道數。

布線格點指的是布局布線中走線規則下垂直水準方向上的交叉節點,如圖3-6所示。

1.?格點間距設定

格點間距可以根據3種形式來設定,即線與線距離、線與通孔距離、通孔與通孔距離,如圖3-7所示。

1)線與線距離。線與線距離是布線金屬層之間的最小drc間距,基于滿足線與線距離的格點間距定義可以最大化地利用走線資源。由于各層金屬之間會通過通孔進行連接配接,如果通孔的面積小于金屬線的寬度,那麼就不會出現drc違反,但是如果通孔的面積大于金屬線寬,布局布線中會由于金屬線到通孔的間距無法滿足最小drc間距的要求而導緻drc違反。

2)線與通孔距離。當通孔的面積大于金屬線寬的時候,線與通孔距離是布線金屬層與通孔之間的最小drc間距,基于滿足線與通孔距離的格點間距定義也可以比較高效地利用走線資源,但是和線與線距離存在的問題一樣,當相鄰的金屬線在相同水準或者垂直方向上同時存在同類型的通孔時,可能出現通孔之間最小間距drc違反,是以在走線資源的任何位置不能随意地通過通孔進行金屬線層與層之間的連接配接,需要布局布線工具通過算法來控制通孔之間最小間距,防止drc違反情況的發生。

3)通孔與通孔距離。當通孔的面積大于金屬線寬的時候,通孔與通孔距離所利用的走線資源比前面兩種格點間距的定義方法要少,但是卻能很好地解決前面兩種格點間距無法解決的最小間距drc問題。定義格點間距滿足通孔與通孔距離後,布局布線工具可以非常靈活地在走線資源的任何位置進行金屬線層與層之間的連接配接并不會出現最小間距drc問題。

2.?垂直水準布線規則設定

垂直水準布線規則定義了金屬層走線方向、走線金屬寬度,走線金屬間距和走線通道偏移值。金屬層走線方向定義後,信号線走線時的方向改變可基于多層金屬走線并通過錯層切換走線方向的方式實作。走線金屬寬度應該大于drc規則的最小金屬寬度,走線金屬間距與格點間距相關。

走線通道偏移值定義了走線通道是否從原點開始還是偏移一定距離,走線通道偏移值分為水準和垂直兩個方向上的定義,如圖3-8所示為水準方向上走線通道偏移值為0和半個格點距離的對比圖。

圖3-9所示為垂直方向上走線通道偏移值為0和半個格點距離的對比圖。

一般情況下,為了能夠在标準單元拼接後得到更好的布局結構且有效地利用布線資源,垂直和水準走線通道都設定了偏移半個格點的間距(如果無偏移,最邊的走線通道隻有一邊有标準單元,資源有些浪費),如圖3-10所示。

同時标準單元的高度應該是垂直方向上的格點間距的整數倍,單元寬度應該是水準方向上格點間距的整數倍,标準單元的有效端口位置應該位于格點上。

标準單元端口分為信号端口和電源端口兩類,基于标準單元自身版圖的特殊要求,需要對這兩類端口進行不同的設定。

1.?标準單元信号端口

标準單元的信号端口即輸入輸出pin腳,如圖3-11所示,輸入輸出pin腳應該在垂直與水準布線通道的交界處,即格點處。布局布線工具可以對沒有在格點的pin腳進行連線,但是這樣會增加布線的難度同時降低布線的效率,作為最基本同時又是使用率最高的基礎單元應該盡量符合高效布線政策的要求。

在标準單元設計時為了提高可連接配接性,信号端口應該分别在水準垂直方向上錯開放置,這樣可以提高布線通道的使用率。同時可以擴大信号端口的金屬層面積,達到覆寫多個格點來提高連通性的目的。

一個具體的标準單元pin腳在格點上的示例如圖3-12所示。

圖3-12中的标準單元,輸入pin腳ck和d端口以及輸出pin腳q端口都處在垂直和水準布線通道的格點上,同時有的端口金屬層覆寫多個格點。

2.?标準單元電源端口

在标準單元庫中,所有單元都是同一高度的。單元版圖允許背靠背的連接配接來分享電源和地線,是以标準單元的電源端口vss和vdd在單元拼接時,由于單元背靠背或者相鄰連接配接就自動拼接在一起了。由于上下相鄰背靠背,上下相鄰兩行的電源/地線自動拼接。由于左右肩并肩相鄰,左右相鄰的标準單元電源/地線自動拼接。如果左右沒有肩并肩緊緊相連,後續會插入填充單元來使同一行上的标準單元肩并肩緊緊相連,達到電源地線連接配接的目的。

标準單元的vdd與vss金屬線進行無縫拼接如圖3-13所示。

圖3-13所示的金屬層3和金屬層5用于水準走線、金屬層4用于垂直走線,通過單元端口的錯開放置有效提高了布線通道使用率。标準單元的vdd與vss金屬線通過上下兩個方位的單元進行無縫拼接。标準單元拼接時陣列間沒有間隔,這使面積減少到最小,但是對于阻塞比較嚴重的設計,不得不在标準單元行之間設定間距來增加足夠的布線通道,如圖3-14所示。

由于預設的标準單元庫設定的初衷是單元背靠背的邊界重疊共享電源地金屬線,但設定了行間距後可能引起drc違反,是以目前主流生産工藝的設計一般不設定标準單元行間距,如果一定要隔開标準單元行,那麼需要人工避免标準單元行可能出現的drc違反。

傳播延時是标準單元本征延時、基于負載大小的延時及基于輸入激勵轉換速度的延時的總稱。傳播延時的大小一般定義為輸入激勵的電源電壓改變50%的點與輸出電壓改變到電源電壓50%的點的時間間隔,但是該定義中的電源電壓改變的參考點可以根據具體工程應用靈活調整。如圖3-15所示為傳播延時的定義。

輸入與輸出的轉換延時一般定義為信号電壓從原始電源電壓的10%變化到電源電壓90%的時間間隔,同樣該定義中的電源電壓參考點可以根據具體的工程應該靈活調整。如圖3-16所示為轉換時間上升與下降時的定義。

影響傳播延時與轉換延時的因素包括:溫度、供電電壓、工藝變化、扇出負載大小、互連負載大小、輸入激勵轉換時間、輸入信号的極性(上升或下降)及時序限制。在時序模型中提供包含有輸入激勵轉換時間對傳播延時的影響資訊,該資訊在時序模型中是以查找表的形式提供的。

衰減因子是指時序資料受工作環境影響而适當乘以的縮放系數。衰減因子由許多不同的标準單元在不同影響程度下,實測資料統計出來的平均值。但是該因子并不适合所有的單元,有些特殊組合的單元可能要好于或壞于該計算結果。

下面我們讨論一下單元延時的計算。當傳播延時、輸出負載、衰減因子确定後,就可以通過下面的計算公式預估出單元總的傳播延時,計算公式如下:

時序參數的定義是指為了保證單元能夠實作正确的邏輯功能所規定的時序限制資訊。時序限制資訊包括:建立時間、保持時間,恢複時間及最小脈沖寬度。

時序限制會影響傳播延。本征延時的計算是基于比較寬松的時序限制(遠大于建立時間、保持時間、恢複時間及脈沖寬度)定義的。在較嚴格的時序限制下,單元需要滿足正确完成邏輯功能的延時小于該時序限制下規定的延時要求。

1.?建立時間

對于時序單元,建立時間是指為了保持單元功能的正确性,輸入資料應該在時鐘信号有效前到達并保持的最小時間。建立時間的測量值定義為資料信号的電壓達到标準電壓50%時間點到時鐘信号電壓到達标準電壓50%時間點的時間間隔。為了測量建立時間,資料信号需要保證時鐘沿有效後的保持時間是無限長的。圖3-17說明建立時間的定義。

2.?保持時間

保持時間是指時序單元要實作正确的邏輯功能,資料在時鐘沿有效後必須保持的最小時間長度。保持時間的測量值定義為資料信号的電壓達到标準電壓50%的時的間點到時鐘信号電壓到達标準電壓50%的時間點的時間間隔。為了測量保持時間,資料信号需要保證時鐘沿有效前的建立時間是無限長的。圖3-18說明保持時間的定義。

3.?恢複時間

恢複時間是指為了保證單元正确的邏輯功能,要求複位/置位信号在時鐘有效沿之前保持有效的最小時間長度。恢複時間的測量值定義為複位或清零信号的電壓達到标準電壓50%的時間點到時鐘信号電壓到達标準電壓50%的時間點的時間間隔。恢複時間的測量需要保證複位或清零信号在時鐘沿有效後保持無限長的保持時間。圖3-19為恢複時間的定義。

4.?移除時間

移除時間是指為了保證單元正确的邏輯功能,要求複位/置位信号在時鐘有效沿之後繼續保持有效的最小時間長度。移除時間的測量值定義為時鐘信号電壓達到标準電壓50%的時間點到複位或清零信号的電壓到達标準電壓50%的時間點的時間間隔。移除時間的測量需要保證複位或清零信号在時鐘沿有效前保持無限長的建立時間。圖3-20為移除時間的定義。

最小脈沖寬度是指脈沖信号波形的開始到結束之間的最小時間間隔。最小高電平脈沖寬度測量值定義為信号的上升沿電壓達到标準電壓50%的時間點到信号電壓下降沿到達标準電壓50%的時間點的時間間隔。最小低電平脈沖寬度測量值定義為信号的下降沿電壓達到标準電壓50%的時間點到信号電壓上升沿到達标準電壓50%的時間點的時間間隔。圖3-21為最小脈沖寬度的定義。

所有對标準單元的時序測量都必須大于最小脈沖寬度,比如當輸入信号的脈沖小于最小脈沖寬度時,測量結果會出錯。

單元在根據輸入信号的變化進行邏輯求值運算中損耗的内在功耗主要由單元的自身結構和功能決定。對設計的功耗計算是一個與單元輸入輸出情況和工作頻率相關的函數。輸入輸出情況包含輸出與輸出端口及所有的輸出負載。

功耗計算

功耗計算的結果基于供電電源的電壓、運作頻率、内部電容及輸出負載。功耗計算公式如下:

式中 pavg——平均功耗;

x——輸入管腳的數量;

y——輸出管腳的數量;

ein——對應輸入管腳消耗的與開關頻率相關的機關功耗;

f?in——在正常工作頻率下輸入管腳的開關頻率;

con——某輸出管腳的外部負載,包括所有輸出管腳與輸出驅動相連的電容、外加的布線金屬走線電容、實際或預估的負載;

vdd——實際工作的理想電壓;

fon——在正常工作頻率下輸出管腳的開關頻率;

eos——輸出管腳所消耗的與開關頻率相關的機關功耗。

通過門級模拟器對典型的輸入管腳進行模拟并測量所有相關節點的變化結果來獲得單元輸入管腳與特殊單元輸出管腳的開關頻率。總的平均功耗通過把所有端口的平均功耗相加而得。

例3.1 觸發器dff單元的功耗計算。

假設觸發器單元時鐘端的開關頻率為133mhz(時鐘頻率為66.5mhz),資料輸入與輸出管腳的開關頻率都為20mhz,輸出管腳的外部負載為0.02pf。使用交流功耗查找表提供dff的基本功耗資料,dff單元的功耗計算使用如下公式:

參數設定如下:

通過公式可以得到平均功耗為1.46uw: