本節書摘來自華章出版社《深入淺出dpdk》一書中的第1章,第1.4節探索ia處理器上最艱巨的任務,作者朱河清,梁存銘,胡雪焜,曹水 等,更多章節内容可以通路雲栖社群“華章計算機”公衆号檢視。

1.4 探索ia處理器上最艱巨的任務

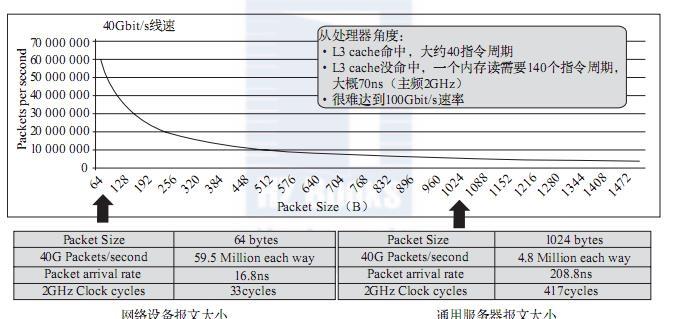

在通用處理器上處理包的最大挑戰是什麼?為什麼以往通用處理器很少在資料面中扮演重要的角色?如果我們帶着這些問題來看資料面上的負載,就會有一個比較直覺的了解。這裡拿40gbit/s的速率作為考察包轉發能力的樣本。如圖1-8所示,曲線為不同大小的包的最大理論轉發能力。

分别截取64b和1024b資料包長,圖1-8所示的線速情況下的封包的指令成本能明顯地說明不同封包大小給系統帶來的巨大差異。就如我們在包轉發率那一節中了解的,對于越小的包,相鄰包到達的時間間隔就越小,16.8ns vs 208.8ns。假設cpu的主頻率是2ghz,要達到理論最大的轉發能力,對于64b和1024b軟體分别允許消耗33和417個時鐘周期。在存儲轉發(store-forward)模型下,封包收發以及查表都需要訪存。那就對比一下訪存的時鐘周期,一次llc命中需要大約40個時鐘周期,如果llc未命中,一次記憶體的讀就需要70ns。換句話說,對于64b大小的包,即使每次都能命中llc,40個時鐘周期依然離33有距離。顯然,小包處理時延對于通用cpu系統架構的挑戰是巨大的。

那是否說明ia就完全不适合高性能的網絡負載呢?答案是否定的。證明這樣的結論我們從兩個方面入手,一個是ia平台實際能提供的最大能力,另一個是這個能力是否足以應對一定領域的高性能網絡負載。

dpdk的出現充分釋放了ia平台對包處理的吞吐能力。我們知道,随着吞吐率的上升,中斷觸發的開銷是不能忍受的,dpdk通過一系列軟體優化方法(大頁利用,cache對齊,線程綁定,numa感覺,記憶體通道交叉通路,無鎖化資料結構,預取,simd指令利用等)利用ia平台硬體特性,提供完整的底層開發支援庫。使得單核三層轉發可以輕松地突破小包30mpps,随着cpu封裝的核數越來越多,支援的pcie通道數越來越多,整系統的三層轉發吞吐在2路cpu的xeon e5-2658 v3上可以達到300mpps。這已經是一個相當可觀的轉發吞吐能力了。

雖然這個能力不足以覆寫網絡中所有端到端的裝置場景,但無論在核心網接入側,還是在資料中心網絡中,都已經可以覆寫相當多的場景。

随着資料面可軟化的發生,資料面的設計、開發、驗證乃至部署會發生一系列的變化。首先,可以采用通用伺服器平台,降低專門硬體設計成本;其次,基于c語言的開發,就程式員數量以及整個生态都要比專門硬體開發更豐富;另外,靈活可程式設計的資料面部署也給網絡功能虛拟化(nfv)帶來了可能,更會進一步推進軟體定義網絡(sdn)的全面展開。