信邁科技以邏輯語言為基礎編寫的H.264視訊編解碼,以IP核的形式,在FPGA器件上運作,基于FPGA的解決方案使用FPGA為核心器件,實作H.264編解碼的IP核,此解決方案為純硬體的解決方案,啟動時間可以忽略,編碼延遲為0.5ms.

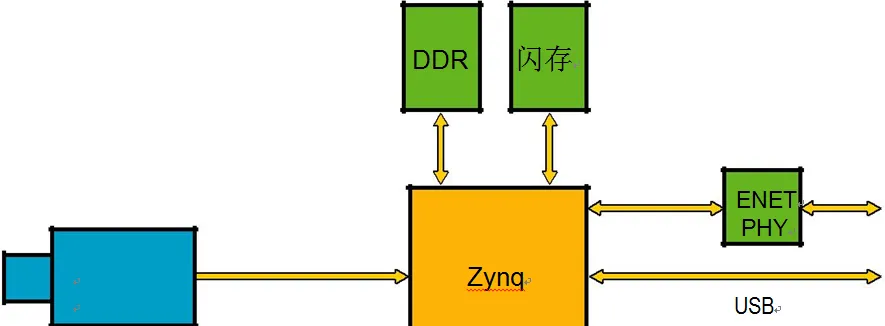

ASSP架構不靈活,而基于FPGA微處理器組合的系統雖然尺寸大但較為靈活,一直以來設計人員為建立PCB占位面積小的基于IP的流式視訊系統,除了在這兩者之間反複權衡外别無他選。将軟核微處理器內建到FPGA,就無需單獨的處理器和DRAM,但最終系統的性能可能無法與以外部ARM®處理器為核心且可能還包括USB、以太網及其它有用外設建構的解決方案所提供的性能相媲美。随着賽靈思Zynq®-7000 All Programmable SoC 和小型H.264核的問世,現在僅用一組DRAM就可在超小型PCB闆上建構出一個具有用多條高速AXI4總線連接配接起來的ARM雙核和高速外設所實作的高性能的系統(見圖1)。

雖然針對FPGA的H.264核問世已有相當長的一段時間,但至今仍沒有一款H.264核夠快夠小,能夠達到足以轉換1080p30幀視訊的水準,而且仍舊适用于小型低成本器件。将Xinmai Technologies公司的最新微型H.264核與Zynq SoC結合使用,可建構一種低延遲時間系統,該系統能夠以15-60fps的不同幀速率對720p-4K之間的多種視訊流進行編/解碼。将Xinmai Technologies H.264核內建到Zynq SoC器件中,可大幅縮減闆級空間并明顯減少元件數,同時在Zynq SoC內建ARM雙核還可避免使用單獨的微處理器及其必須連接配接的存儲體。

圖1 - 基于單晶片 Zynq SoC的視訊壓縮系統 (上)與基于雙晶片處理器和FPGA的視訊壓縮系統對比

這樣可以建構出一個以Linux驅動程式和實時流協定(RTSP)伺服器為核心的完整流式視訊系統,該系統能夠對來自兩個攝像頭的1080p30幀視訊進行壓縮,且端到端時延約為10毫秒。Xinmai Technologies H.264核提供純編碼版和編/解碼版兩個版本。此外,還有一款低延遲時間版本,可将編碼時延降至5毫秒以下。1080p30純編碼版需要10000個查找表(LUT),或者說會占用Zynq Z7020 FPGA架構25%左右的資源,而編/解碼版則需要11,000個查找表。

基于SOC-FPGA的系統

基于Zynq SoC的産品比采用特定應用标準産品(ASSP)建構的産品靈活性更高。例如,通過在FPGA架構中内置4個H.264核,并将每個攝像頭輸入端連接配接到FPGA,就可以很容易建構一個支援1080p30輸入的系統。許多ASSP産品隻有兩個輸入端,這讓設計人員不得不想辦法多路複用若幹視訊流到一個輸入端。每個Xinmai Technologies H.264核能夠處理六個VGA分辨率攝像頭或一個1080p30分辨率攝像頭。是以,有可能建構一個雙核系統,以便對來自12個VGA攝像頭輸入的視訊進行壓縮。

ASSP産品通常僅對已解碼視訊提供螢幕視控(OSD)功能,這迫使設計人員将OSD資訊作為中繼資料發送或使用ARM核心測定視訊幀時間并以程式設計方式将OSD資料寫入視訊緩沖區。在FPGA中,在進行視訊壓縮前添加OSD如同通路IP子產品一樣簡單。同時在壓縮引擎前添加魚眼鏡頭校正等其它處理子產品,也相對容易。此外,FPGA還支援功能的現場與未來更新,例如添加H.265 壓縮功能。圖2是帶有兩個1080p30攝像頭輸入的H.264壓縮引擎方框圖,其中OSD适用于未壓縮圖像。

如何應對延時

某些應用程式,如遙控飛行器(RPV)的控制,是基于遙控裝置發回的流媒體圖像回報。為了控制遙控裝置,從傳感器發送視訊至壓縮引擎到解碼圖像顯示(稱為“玻璃對玻璃”)之間的時延通常要小于100毫秒。一些設計人員将時延規定在50毫秒内。總時延是如下幾項的和:

視訊處理時間(ISP、魚眼鏡頭校正等)

•填充幀緩沖的延遲

•壓縮時間

•發送資料包引起的軟體延遲

•網絡延遲

•接收資料包引起的軟體延遲

•視訊解碼時間

許多系統采用硬體對視訊進行編碼,但最終卻采用标準的視訊播放器進行解碼,如在PC上運作的VLC。即使媒體播放器的緩沖延遲可從一般的500-1000毫秒大幅減少,但時延仍然遠遠超過50毫秒。要真正控制時延并保持在絕對最低水準,就需要對已壓縮視訊流進行硬體解碼,而且要求緩沖最小。

H.264編碼器時延通常以幀來表示,如一般在壓縮開始前必須緩沖一個完整幀的時間。假設編碼器速度可以提高,那麼僅通過幀速率加倍即可降低編碼時延,也就是說,幀速率為30fps時每幀時延為33毫秒,而幀速率為60fps時每幀時延則為16.5毫秒。

很多時候,由于錄影機和編碼器的性能限制該方案無法實施。是以,該解決方案是專門設計用于低延編碼器。而最新Xinmai Technologies低延時編碼器隻有16個視訊線才需要在壓縮開始前進行緩沖。對于1080p30視訊流而言,時延不足500微秒(µs)。而對于480p30視訊流而言,時延則低于1毫秒。設計人員采用這種低延遲時間編碼器可建構出時延可預測且很低的系統。

為使總時延最小化,必須同時最大限度地降低編碼側和解碼側上緩沖、網絡協定棧、RTSP伺服器/用戶端等引起的時延,因為軟體路徑會産生很長的時延,而在這種情況下采用低延遲時間編碼器毫無意義。RTSP伺服器通常用來在伺服器(攝像頭)與用戶端(解碼/記錄)裝置之間建立流式視訊連接配接。連接配接建立後,RTSP伺服器會将壓縮的視訊傳送至用戶端以供顯示或存儲。

延時最小低化時延

通常情況下,伺服器和用戶端的軟體元件隻要求與帶寬比對,友善傳送壓縮視訊,而不是為了最小化時延。而如Linux之類的非實時作業系統則很難保證時延。典型的解決方案就是為伺服器和用戶端建立低延遲時間自定義協定。但這種方法的不足之處就是不符合行業标準。另一種方法是采用一種類似RTSP的标準,通過對軟體的低層進行修改來最小化時延,同時保證符合各項标準。

然而,也可采取措施盡量減少核心與使用者空間之間的拷貝操作,進而減少相關時延。

圖3 完整編/解碼系統方框圖

而就整個軟體路徑而言,要減少時延,就需要将RTSP伺服器和壓縮資訊轉發任務分離,進而用Linux驅動程式替代RTSP伺服器執行發送任務。

為了降低延遲時間,我們對Xinmai Technologies低延遲時間RTSP伺服器進行了兩處修改。首先,移除轉發路徑上的RTSP伺服器。RTSP伺服器仍采用實時控制協定(RTCP)維護統計資料,并随網絡目标位址(即IP或MAC目的地位址)的變動定期(或異步)更新核心驅動。第二,核心驅動程式附加必要資料頭(基于RTSP伺服器提供的資訊),通過直接輸入網絡驅動程式(例如udp_send)立即轉發資料包,進而無需在核心和使用者空間之間進行記憶體拷貝。

圖3 顯示了基于H.264 IP的完整編/解碼系統,總時延不足50毫秒。該系統是根據Zynq SoC、Xinmai Technologies低延遲時間H.264編/解碼器與Xinmai Technologies 低延遲時間RTSP伺服器/用戶端而建立的。需要注意的是,從硬體角度來看,編碼與解碼系統之間唯一真正的差別在于,編碼側必須連接配接到攝像頭/傳感器,而解碼側則必須能夠為平闆顯示提供驅動。您可以輕松地設計一個具備編碼與解碼所需的所有必備硬體功能的電路闆。

為盡量減少實時控制應用中視訊壓縮/解壓縮的時延,設計人員需要特殊編碼器和優化的軟體。利用賽靈思的Zynq SoC和 Xinmai Technologies的H.264低延遲時間編碼器與以及優化的RTSP 伺服器/用戶端,可在小型PCB闆上建立一個時延極低、高度可配置的系統。

1 評估闆簡介

信邁科技 XM-ZYNQ7045-EVM 是一款基Xilinx Zynq-7000 系列 XC7Z045/XC7Z100 高性能處理器設計的高端異構多核 SoC 評估闆,處理器內建 PS 端雙核 ARM Cortex-A9 + PL 端 Kintex-7 架構 28nm 可程式設計邏輯資源,評估闆由核心闆與評估底闆組成。核心闆經過專業的 PCB Layout 和高低溫測試驗證,穩定可靠,可滿足各種工業應用環境。

評估闆接口資源豐富,引出雙路千兆網口、四路 SFP+光口、CameraLink、HDMI、F

MC HPC、GTX、PCIe、USB、Micro SD 等接口,友善使用者快速進行産品方案評估與技術

預研。

圖 1 Xilinx Zynq-7000 處理器功能框圖

圖2

圖3

圖4

圖5

2 典型應用領域

- 軟體無線電

- 雷達探測

- 光電探測

- 視訊追蹤

- 圖像處理

- 水下探測

- 定位導航

- 深度學習

3 軟硬體參數

3.1 硬體參數

表1

| CPU | CPU:Xilinx Zynq-7000 XC7Z045/XC7Z100-2FFG900I |

| 2x ARM Cortex-A9,主頻 800MHz,2.5DMIPS/MHz Per Core | |

| 1x Kintex-7 架構可程式設計邏輯資源 | |

| ROM | PS 端:8GByte eMMC |

| PS 端:128/256Mbit SPI NOR FLASH | |

| RAM | PS:單通道 32bit DDR 總線,1GByte DDR3 |

| PL:單通道 32bit DDR 總線,1/2GByte DDR3 | |

| Logic Cell | XC7Z045:350K,XC7Z100:444K |

| OSC | PS 端:33.33MHz |

| B2B Connector | 2x 140pin 公座高速 B2B 連接配接器,2x 140pin 母座高速 B2B 連接配接器,共 560pin, 間距 0.5mm,合高 7.0mm |

| LED | 2x 電源訓示燈(核心闆 1 個,評估底闆 1 個) |

| 1x PL 端 DONE 燈(核心闆 1 個) | |

| 3x PS 端使用者可程式設計訓示燈(核心闆 2 個,評估底闆 1 個) | |

| 2x PL 端使用者可程式設計訓示燈(評估底闆 2 個) | |

| KEY | 1x 電源複位按鍵 |

| 1x 系統複位按鍵 | |

| 1x PS 端使用者輸入按鍵 | |

| 1x PL 端使用者輸入按鍵 | |

| SD | 1x Micro SD 接口(PS 端) |

| XADC | 1x 排針接口,2x 2pin 規格,2.54mm 間距,單通道專用差分輸入,1MSPS |

| Ethernet | 1x PS RGMII,RJ45 接口,10/100/1000M 自适應(PHY 位于核心闆上) |

| 1x PL RGMII,RJ45 接口,10/100/1000M 自适應 | |

| Watchdog | 1x Watchdog,3pin 排針方式,2.54mm 間距,通過跳線帽配置 |

| UART | 1x Debug UART,Micro USB 接口(PS 端) |

| 1x RS232 UART,DB9 接口(PL 端) | |

| 1x RS485 UART,3pin 3.81mm 綠色端子方式(PL 端) | |

| CAN | 2x CAN,3pin 3.81mm 綠色端子方式(PL 端) |

| USB | 4x USB 2.0 HOST 接口,使用 HUB 擴充(PHY 位于核心闆上) |

| PCIe | 1x PCIe,由兩組 GTX 引出,共兩通道,x4 金手指連接配接方式(PL 端) |

| IO | 1x 400pin FMC 連接配接器,1.27mm 間距,HPC 标準 |

| SATA | 1x 7pin SATA 接口,150MHz LVDS 差分時鐘(PL 端) |

| HDMI | 1x HDMI OUT(PL 端) |

| 1x HDMI IN(PL 端) | |

| DISPLAY | 1x LCD RES 電阻觸摸屏,40pin FFC 連接配接器,間距 0.5mm(PL 端) |

| CAMERA | 2x CAMERA,2x 10pin 排母方式,間距 2.54mm(PL 端) |

| CameraLink | 2x CameraLink Base 接口,支援 Full 模式(PL 端) |

| SFP+ | 4x SFP+光口,支援萬兆光子產品,由高速串行收發器(GTX)引出 |

| LVDS | 1x 排針接口,2x 15pin 規格,可接通用 LVDS 顯示屏,間距 2.00mm(PL 端) |

| SMA | 1x GTX CLK |

| 1x GTX RX | |

| 1x GTX TX | |

| RTC | 1x RTC 座,适配紐扣電池 ML2032(3V 可充)、CR2032(3V 不可充) |

| FAN | 1x FAN,3pin 排針端子,12V 供電,間距 2.54mm |

| JTAG | 1x 14pin JTAG 接口,間距 2.0mm |

| BOOT SET | 1x 6bit 啟動方式選擇撥碼開關 |

| SWITCH | 1x 電源擺動開關 |

| POWER | 1x 12V6A 直流輸入 DC-005 電源接口,可接外徑 5.5mm、内徑 2.1mm 電源插頭 |

3.2 軟體參數

表 2

| ARM 端軟體支援 | 裸機,FreeRTOS,Linux-4.9.0 | |

| Vivado 版本号 | 2017.4 | |

| 軟體開發套件提供 | PetaLinux-2017.4,Xilinx SDK 2017.4,Xilinx HLS 2017.4 | |

| 驅動支援 | SPI NOR FLASH | DDR3 |

| USB 2.0 | eMMC | |

| LED | KEY | |

| RS485 | MMC/SD | |

| Ethernet | CAN | |

| 7in Touch Screen LCD(Res) | XADC | |

| I2C | USB 4G | |

| USB WIFI | RS232 |

4 開發資料

(1)提供核心闆引腳定義、可編輯底闆原理圖、可編輯底闆 PCB、晶片 Datasheet,縮短

硬體設計周期;

(2)提供系統固化鏡像、核心驅動源碼、檔案系統源碼,以及豐富的 Demo 程式;

(3)提供完整的平台開發包、入門教程,節省軟體整理時間,讓應用開發更簡單;

(4)提供詳細的 PS + PL SoC 架構通信教程,完美解決異構多核開發瓶頸。

開發案例主要包括: Ø

- 基于 Linux 的開發例程

- 基于裸機的開發案例

- 基于 FreeRTOS 的開發案例

- 基于 PS + PL 的異構多核開發案例

- 基于 OpenAMP 的 Linux + 裸機/FreeRTOS 雙核 ARM 通信開發案例

- 基于 PL 端的 HDL、HLS 開發案例

- Qt 開發案例

- CameraLink、SDI、HDMI、PAL 視訊輸入/輸出案例

- 高速 AD(AD9613)采集 + 高速 DA(AD9706)輸出案例

- AD9361 軟體無線電案例

- UDP(10G)光口通信案例

- Aurora 光口通信案例

- PCIe 通信案例

5 電氣特性

工作環境

| 環境參數 | 最小值 | 典型值 | 最大值 |

| 核心闆工作溫度 | -40°C | / | 85°C |

| 核心闆工作電壓 | / | 5.0V | / |

| 評估闆工作電壓 | / | 12.0V | / |

功耗測試

| 類别 | 工作狀态 | 電壓典型值 | 電流典型值 | 功耗典型值 |

| 核心闆 | 狀态 1 | 5.0v | 0.40A | 2.00W |

| 狀态 2 | 5.0v | 1.85A | 9.25W | |

| 評估闆 | 狀态 1 | 12.0v | 0.43A | 5.16W |

| 狀态 2 | 12.0v | 1.19A | 14.28W |

備注:功耗基于 CPU 為 XC7Z045 的核心闆測得。功耗測試資料與具體應用場景有關,測試資料僅供參考。

狀态 1:評估闆不接入外接子產品,PS 端啟動系統,不執行額外應用程式;PL 端運作 LED 測試程式。

狀态 2:評估闆不接入外接子產品,PS 端啟動系統,運作 DDR 壓力讀寫測試程式,2 個 ARM Cortex-A9核心的資源使用率約為 100%;PL 端運作 IFD 綜合測試程式。

圖 11 狀态 2 資源使用率

6機械尺寸

表 4

| 核心闆 | 評估底闆 | |

| PCB 尺寸 | 62mm*100mm | 142.75mm*260mm |

| PCB 層數 | 14 層 | 8 層 |

| PCB 闆厚 | 1.6mm | 1.6mm |

| 安裝孔數量 | 4 | 4 |

圖 12 核心闆機械尺寸圖

7技術服務

- 協助底闆設計和測試,減少硬體設計失誤;

- 協助解決按照使用者手冊操作出現的異常問題;

- 協助産品故障判定;

- 協助正确編譯與運作所提供的源代碼;

- 協助進行産品二次開發;

- 提供長期的售後服務。

8增值服務

- 主機闆定制設計

- 核心闆定制設計

- 嵌入式軟體開發

- 項目合作開發

- 技術教育訓練