基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem實作了基于DMA位址隊列的高性能Continous或Scather Gather DMA,提供FIFO/AXI4-Stream使用者接口。

可傳遞資料:

- 詳細的使用者手冊

- Design File:Post-synthesis EDIF netlist or RTL Source

- Timing and layout constraints,Test or Design Example Project

- 技術支援:郵件,電話,現場,教育訓練服務

聯系方式:

Email:[email protected]

1 介紹

1.1 特性

- 支援Ultrascale+,Ultrascale,7 Series的PCI Express Integrated Block

- 支援64,128,256,512-bit資料路徑

- 64-bit源位址,目的位址,和描述符位址

- 多達16個host-to-card(H2C/Read)資料通道或H2C DMA

- 多達16個card-to-host(C2H/Write)資料通道或C2H DMA

- FIFO/ AXI4-Stream使用者接口(每個通道都有自己的FIFO/AXI4-Stream接口)

- 每個DMA引擎支援DMA位址隊列,隊列深度可達32

- AXI4-Lite Master接口允許PCIe通信繞過DMA引擎

- Scather Gather描述符清單支援無限清單大小

- 每個描述符的最大傳輸長度為4GB

- MSI中斷

- 連續描述符的塊擷取

- 中斷或查詢模式

1.2 應用

本核心體系結構支援廣泛的計算和通信目标程式應用,強調性能、成本、可擴充性、功能可擴充性和關鍵任務可靠性。典型應用包括:

● 資料通信網絡

● 電信網絡

● 寬帶有線和無線應用

● 網絡接口卡

● 用于各種應用程式的伺服器add-in card

典型應用如下圖所示:

圖 1 Multi-Channel PCIe QDMA Subsystem典型應用:8通道視訊采集和視訊顯示

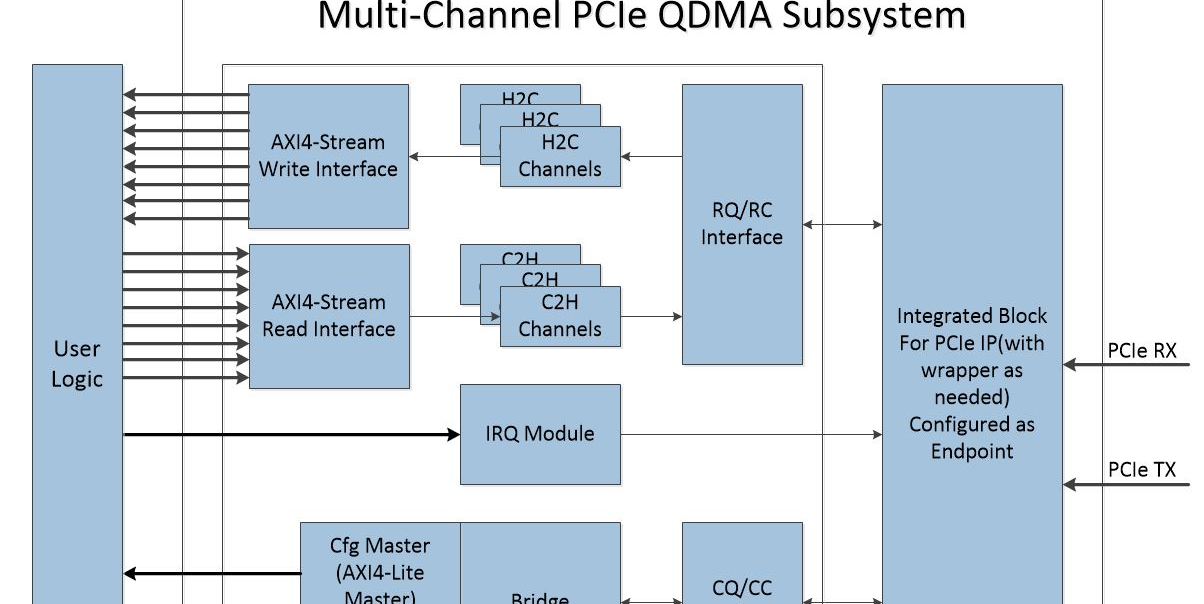

2 概述

Multi-Channel PCIe QDMA Subsystem作為一個高性能DMA資料搬移器,核心通過AXI4-Stream接口直接連接配接RTL邏輯。使用提供的字元驅動程式,AXI4-Stream接口可用于PCIe位址空間和AXI位址空間之間的高性能資料搬移。除了基本的DMA功能,DMA支援多達16個upstream和downstream通道,每個通道支援深度為32的DMA位址隊列,另外還允許PCIe通信繞過DMA引擎。

圖 2 Multi-Channel PCIe QDMA Subsystem概述

2.1 特性概要

基于描述符提供的資訊:源位址,目的位址和傳輸資料長度,Multi-Channel PCIe QDMA Subsystem實作Host存儲器和PCIe DMA子系統之間的資料搬移。這些DMA可以同時是Host to Card(H2C)和Card to Host(C2H)傳輸。每個DMA通道對應各自的AX4-Stream接口,DMA從Host存儲器擷取并解析描述符連結清單,基于描述符連結清單資訊完成自己通道的資料傳輸,然後使用MSI中斷發出描述符完成或錯誤的信令。核心也提供多達16個輸出到Host的使用者中斷信号。

主機可以通過以下2個接口通路使用者邏輯:

- AXI-Lite Master配置接口:這個接口是一個固定的32-bit端口,用于對性能要求不高的使用者配置和狀态寄存器的通路

- User Register:這個接口是多個32-bit向量信号和1-bit信号,這些信号來自對應DMA通道資料搬移過程中産生的控制或狀态信号

3 産品規格

結合Integrated Block for PCI Express IP,Multi-Channel PCIe QDMA Subsystem為PCIe提供了一個高性能的DMA解決方案。

3.1 性能

Endpoint配置參數:Max Payload Size=256-byte,Max Read Request Size=512-byte

8-Channel PCIe-SGQDMA Subsystem,DMA Transfer Length = 4MB

表1 PCIe 3.0 x16 C2H DMA速率

| DMA0 | DMA1 | DMA2 | DMA3 | DMA4 | DMA5 | DMA6 | DMA7 | |

| 速率 | 1660MB/s |

表2 PCIe 3.0 x16 H2C DMA速率

| 1670MB/s |

表3 PCIe 3.0 x8 C2H DMA速率

| 880MB/s |

表4 PCIe 3.0 x8 H2C DMA速率

| 890MB/s |

表5 PCIe 2.0 x8 C2H DMA速率

| 450MB/s |

表6 PCIe 2.0 x8 H2C DMA速率

| 455MB/s |

3.2 資源

8-Channel PCIe-SGQDMA Subsystem

表7 PCIe 3.0 x16 DMA Subsystem資源

| LUTs | FFs | BRAMs | PCIe | |

| 資源 | 46985 | 101938 | 150 | 1 |

表8 PCIe 3.0 x8 DMA Subsystem資源

| 26388 | 51935 | 78 |

表9 PCIe 2.0 x8 DMA Subsystem資源

| 26945 | 38687 | 55 |

8-Channel PCIe-CQDMA Subsystem

表10 PCIe 3.0 x16 DMA Subsystem資源

| 34976 | 75994 |

表11 PCIe 3.0 x8 DMA Subsystem資源

| 19364 | 37487 |

表12 PCIe 2.0 x8 DMA Subsystem資源

| 20973 | 29963 |

3.3 核心Component

核心内部實作多達32個獨立的實體DMA引擎(多達16個C2H和16個H2C)。這些DMA引擎被映射到各自的AXI4-Stream使用者應用接口。AXI4-Stream接口隻傳遞資料。

通道的類型配置決定了在哪個總線上進行事務傳輸。

- Host-to-Card(H2C)通道向PCIe産生讀請求,然後給使用者應用提供資料

- 同樣,Card-to-Host(C2H)通道等待使用者側的資料,然後向PCIe産生寫請求(包含接收到的資料)

Host通過AXI4-Lite Master接口通路使用者邏輯的配置和狀态寄存器。這些請求是32-bit的讀或寫。

3.3.1 Target Bridge

Target bridge從Host接收請求。基于BARs,這些請求通過AXI4-Lite Master接口傳遞到内部的目标使用者。下行使用者邏輯傳回non-post請求的資料後,target bridge産生一個讀傳回TLP,然後通過CC總線發送給PCIe IP。

PCIe BARs配置如下表所示。

表13 32-bit BARs

| BAR0(32-bit) | BAR1(32-bit) |

| DMA | PCIe to AXI4-Lite Master |

3.3.2 H2C通道

H2C通道處理host-to-card的DMA傳輸。根據最大讀請求大小和可用的内部資源,H2C通道負責拆分這些讀請求。讀取請求的每個拆分(如果有)都會消耗一條額外的讀取請求條目。DMA通道向PCIe RQ子產品發出讀請求後,直到按順序接收到使用者接口的寫完成确認,這個讀請求才算完成。在資料傳輸完成後,DMA通道向Host發出一個中斷。

H2C通道會根據配置的最大讀請求大小和資料FIFO可用空間來拆分Host讀接口上的資料傳輸。從PCIe RC子產品輸出的讀請求傳回完成資料包會存儲到已配置設定的資料FIFO中。為了減少資料傳輸延時,一旦接收到任何一個完成資料包,H2C通道就開始把讀取的資料輸出到AXI4-Stream Write接口。

3.3.3 C2H通道

C2H通道處理card-to-host的DMA傳輸。在AXI4-Stream Read接口接收資料之前,C2H通道首先接收DMA描述符,建立DMA傳輸的環境,然後在準備好請求ID和啟用C2H通道後,通道的AXI4-Stream接口可以接收資料并對主機執行DMA。在資料傳輸完成後,DMA通道向Host發出一個中斷。

3.3.4 AXI4-Lite Master

Host使用這個接口向使用者邏輯發出32-bit讀和32-bit寫請求。通過PCIe總線接收讀或者寫請求,路由到AXI-Lite Master BAR中,target bridge通過PCIe IP CC總線傳回讀取的完成資料。

3.3.5 IRQ Module

IRQ module接收來自使用者邏輯中斷請求和每個DMA通道的獨立中斷線。這個子產品通過PCIe向Host産生MSI中斷。

3.3.6 DMA操作

從DMA的原理出發,PCIe DMA引擎通常在Host記憶體和駐留在FPGA中的記憶體之間搬移資料,FPGA的記憶體通常(但不總是)位于add-in闆卡。當資料從Host記憶體搬移到FPGA記憶體時,稱為Host to Card(H2C)傳輸。相反,當資料從FPGA記憶體搬移到Host記憶體,稱為Card to Host(C2H)傳輸。

在通常的操作中,Host中的應用程式必須在FPGA和Host記憶體之間搬移資料。為了完成此次傳輸,Host在系統記憶體中設定緩沖區空間,并建立DMA引擎用于搬移資料的描述符。

Multi-Channel PCIe QDMA Subsystem使用連續的描述符連結清單,單個描述符指定了位址和DMA傳輸長度。Host驅動建立描述符連結清單,并存儲在Host記憶體。Host驅動隻需要少量控制寄存器就可以初始化DMA通道,接着該DMA通道就開始去擷取描述符連結清單并執行DMA操作。

描述符描述了Multi-Channel PCIe QDMA Subsystem執行的記憶體傳輸。每個DMA通道有自己的描述符連結清單。Host驅動通過硬體寄存器初始化每個DMA通道描述符連結清單的起始位址。在啟動DMA通道後,該DMA通道開始從起始位址擷取描述符。

EOP控制比特顯示描述符連結清單的終止。當DMA通道檢測到某個描述符的EOP控制比特後,會停止擷取該描述符連結清單。EOP控制比特隻能在描述符連結清單的最後一個描述符中被設定。

描述符格式如下表所示。

表14 描述符格式

| Offset | Fields |

| 0x0 | Bit 31:EOP Bit 30~16:保留 Bit 15~0:Magic,常數16’hAD4B |

| 0x4 | DMA Transfer Length |

| 0x8 | Address[31:0] |

| 0xC | Address[63:32] |

Address:64-bit,Destination address for C2H或Source address for H2C

EOP:1-bit,End of packet for stream data

DMA Transfer Length:32-bit,Length of data in bytes

3.4 端口描述

Multi-Channel PCIe QDMA Subsystem直接和integrated block for PCIe連接配接。和PCIe integrated block IP資料路徑接口的寬度是64,128,256或512-bit,時鐘頻率最高可達250MHz。除了AXI4-Lite Master接口,資料路徑寬度适用于所有資料接口。AXI4-Lite Master接口的寬度固定為32-bit。

以下清單描述了這個IP的端口(預設資料路徑接口寬度是512-bit,PCIe接口是x16)。

表15 參數定義

| 參數名稱 | 描述 | 預設值 |

| CNUM | H2C和C2H的通道數量 | 8 |

| C2H_BUF_BRAM_CASCADE_DEPTH | C2H資料緩沖區的BRAM級聯深度 0:BRAM深度=29=512 1:BRAM深度=29+1=1024 …… N:BRAM深度=29+N | |

| C2H_BUF_USE_URAM | C2H資料緩沖區是否使用URAM 0:不使用URAM 1:使用URAM | |

| C2H_BUF_URAM_CASCADE_DEPTH | H2C資料緩沖區的URAM級聯深度 0:URAM深度=212=4096 1:URAM深度=212+1=8192 N:URAM深度=212+N | |

| H2C_BUF_BRAM_CASCADE_DEPTH | H2C資料緩沖區的BRAM級聯深度 | |

| H2C_BUF_USE_URAM | H2C資料緩沖區是否使用URAM | |

| H2C_BUF_URAM_CASCADE_DEPTH | C2H資料緩沖區的URAM級聯深度 |

表16 頂層接口信号

| 信号名稱 | 輸入輸出 | |

| pcie_trn_clk | 輸出 | PCI Express Transaction接口時鐘 |

| pcie_trn_reset_n | PCI Express Transaction複位,低有效 | |

| trn_lnk_up | PCI Express Transaction Link Up信号,高有效 |

表17 PCIe接口信号

| pcie_refclk_p | 輸入 | PCI Express 接口參考時鐘+ |

| pcie_refclk_n | PCI Express 接口參考時鐘- | |

| pcie_perst_n | PCI Express接口基本複位,低有效 | |

| pci_exp_txp[15:0] | PCI Express串行差分輸出+,16通道 | |

| pci_exp_txn[15:0] | PCI Express串行差分輸出-,16通道 | |

| pci_exp_rxp[15:0] | PCI Express串行差分輸入+,16通道 | |

| pci_exp_rxn[15:0] | PCI Express串行差分輸入-,16通道 |

表18 H2C通道0-CNUM-1 FIFO(FWFT)接口信号

| fifo_rdclk_disp [CNUM-1:0] | FIFO讀時鐘 Bit i,表示H2C通道i的讀時鐘 | |

| fifo_rdreq_disp | FIFO讀使能,高有效 Bit i,表示H2C通道i的讀使能 | |

| fifo_q_disp [512*CNUM-1:0] | FIFO讀資料 Bit 512*(i+1)-1~512*i,表示H2C通道i的讀資料 | |

| fifo_empty_disp | FIFO空,高有效 Bit i,表示H2C通道i的緩存空信号 | |

| fifo_prog_empty_disp | FIFO可程式設計空(門檻值等于16),高有效 Bit i,表示H2C通道i的緩存可程式設計空信号 |

表19 C2H通道0-CNUM-1 FIFO接口信号

| fifo_wrclk_acq | FIFO寫時鐘 Bit i,表示C2H通道i的寫時鐘 | |

| fifo_wrreq_acq | FIFO寫使能,高有效 Bit i,表示C2H通道i的寫使能 | |

| fifo_data_acq | FIFO寫資料 Bit 512*(i+1)-1~512*i,表示C2H通道i的寫資料 | |

| fifo_prog_full_acq | FIFO可程式設計滿(門檻值等于深度-16),高有效 Bit i,表示C2H通道i的緩存可程式設計滿信号 |

表20 Config AXI4-Lite Master接口信号

| m_axil_awaddr | write address | |

| m_axil_awprot[2:0] | write protection type | |

| m_axil_awvalid | write address valid | |

| m_axil_awready | write address ready | |

| m_axil_wdata[31:0] | write data | |

| m_axil_wstrb[3:0] | write strobes | |

| m_axil_wvalid | write valid | |

| m_axil_wready | write ready | |

| m_axil_bresp[1:0] | write response | |

| m_axil_bvalid | write response valid | |

| m_axil_bready | response ready | |

| m_axil_araddr[31:0] | read address | |

| m_axil_arprot[2:0] | read protection type | |

| m_axil_arvalid | read address valid | |

| m_axil_arready | read address ready | |

| m_axil_rdata[31:0] | read data | |

| m_axil_rresp[1:0] | read response | |

| m_axil_rvalid | read valid | |

| m_axil_rready | read ready |

表21 中斷接口信号

| usr_intr_pos[15:0] | 使用者中斷輸入。 Bit i:使用者中斷#i輸入,上升沿有效。 |

表22 軟複位接口信号

| sw_srst_n | 軟複位輸出,低有效。 |

表23 使用者寄存器接口信号

| acquisition_res [32*CNUM-1:0] | CNUM個C2H通道的分辨率設定 Bit 32*(i+1)-1~32*i,表示C2H通道i的分辨率 | |

| display_res | CNUM個H2C通道的分辨率設定 Bit 32*(i+1)-1~32*i,表示H2C通道i的分辨率 | |

| acquisition_fps | CNUM個C2H通道的幀率設定 Bit 32*(i+1)-1~32*i,表示C2H通道i的幀率 | |

| display_fps | CNUM個H2C通道的幀率設定 Bit 32*(i+1)-1~32*i,表示H2C通道i的幀率 | |

| acquisition_enable | CNUM個C2H通道的采集使能,高有效 Bit i = 1,表示使能C2H通道i采集 | |

| display_enable | CNUM個H2C通道的顯示使能,高有效 Bit i = 1,表示使能H2C通道i顯示 | |

| acquisition_stat | CNUM個C2H通道的狀态 Bit 32*(i+1)-1~32*i,表示C2H通道i的狀态 | |

| display_stat | CNUM個H2C通道的狀态 Bit 32*(i+1)-1~32*i,表示H2C通道i的狀态 | |

| usr_ctrl[31:0] | 控制信号輸出 | |