10.1 組合邏輯設計

一、組合邏輯控制單元框圖

1.外特性

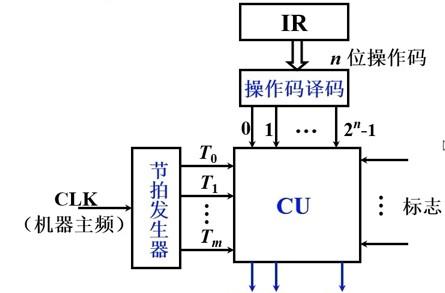

如圖1.1所示,CU要發出各種控制指令,這些信号是由先後關系,每個控制信号發出都是有給定時間點,這種時間點是由節拍控制,是以要有節拍發生器。CU要産生什麼控制指令與現在執行指令有關系,目前指令儲存在IR中,其n位操作碼經過操作碼譯碼後才能确定正在執行是哪條指令。譯碼結果針對每一條指令是一一對應的,輸入到CU中。CU發出什麼信号還和标志有關系,是以輸入還有一系列标志。CU在以上作用下,有輸出C0……Ck。C0……Ck可以有1個或多個高電平,多個高電平有兩種含義:要麼是它們并行,要麼是他們在一個周期,但是它們每一個操作都不夠一個周期。

圖1.1 組合邏輯電路外特性

二、微操作的節拍安排

(1)采用同步控制方式

假設一個機器周期有3個節拍(時鐘周期),CPU采用非總線方式。

1.安排微操作時序的原則

原則一:微操作的先後順序不得随意更改。

原則二:被控對象不同的微操作(可以并行執行的),盡量安排在一個節拍内完成。

原則三:占用時間較短的微操作,盡量安排在一個節拍内完成,并允許有先後順序。

2.取指周期微操作的節拍安排

| T0 | PC->MAR, 1->R | 原則二 |

| T1 | M(MAR)->MDR, (PC)+1->PC | |

| T2 | MDR->Ad(IR), OP(IR)->ID | 原則三 |

3.間址周期微操作的節拍安排

| Ad(IR)->MAR, 1->R | |

| M(MAR)->MDR | |

| MDR->Ad(IR) |

3.執行周期微操作的節拍安排

①非訪存指令

1)清除累加器指令CLA

該指令在執行周期隻有一個微操作,按同步控制的原則,此操作可安排在T0-T2的任一節拍内,其餘節拍空。如在T2周期内安排(T2: 0->AC)。

2)累加器取反指令COM

同理,按同步控制的原則,此操作可安排在T0-T2的任一節拍。

3)算術右移一位指令SHR

同理,按同步控制的原則,此操作可安排在T0-T2的任一節拍。如在T2周期内安排(L(AC)->R(AC), AC0-AC0)。

4)循環左移一位指令CSL

同理,按同步控制的原則,此操作可安排在T0-T2的任一節拍。如在T2周期内安排(R(AC)->L(AC), AC0->ACn)。

5)停機指令STP

| 0->G |

(2)訪存指令

1)加法指令ADD X

| Ad(IR)->MAR,1->R | |

| (AC)+(MDR)->AC |

2)存數指令STA X

| Ad(IR)->MAR,1->W | |

| AC->MDR | |

| MDR->M(MAR) |

3)取數指令LDA X

(3)轉移類指令

1)無條件轉移指令 JMP X

| Ad(IR)->PC |

2)有條件轉移(負則轉)指令 BAN X

4.中斷周期微操作的節拍安排

在執行周期的最後時刻,CPU要向所有中斷源發終端查詢信号,若檢測到某個中斷源有請求,并且未被屏蔽又被排隊選中,則在允許中斷的條件下,CPU進入中斷周期,此時CPU由中斷隐指令完成下列操作(假設程式斷點存入主存0号位址單元内):

| 0->MAR, 1->W(關中斷,可以放在這裡) | |

| PC->MDR(PC中儲存着斷點) | |

| MDR->M(MAR),向量位址->PC |

CPU進入中斷周期,由硬體置“0”允許中斷觸發器EINT,即關中斷。

三、組合邏輯按設計步驟

1.列出操作時間表;

2.寫出微操作指令的最簡邏輯表達式;

3.畫出微操作指令的邏輯圖。

這種方法有以下特點:

(1)思路清晰,簡單明了;

(2)龐雜,調試困難,修改困難;

(3)速度快。

用在精簡中(RISC),通常情況下整型單元也是用這個。

10.2 微程式設計

一、微程式設計思想

一條機器指令對應一個微程式。完成一條機器指令有多個微操作指令,每幾個微操作指令組成一個微指令,這些微指令稱為微程式。

二、微程式控制單元框圖及工作原理

1.機器指令對應的微程式

采用微程式設計方法設計控制單元的過程就是編寫每一條機器指令的微程式,它是按照每條機器指令所需的微操作指令的先後順序而編寫的,是以,一條機器指令對應一個微程式,如圖2.1所示。圖中每一條機器指令都與一個以操作性質命名的微程式對應。

由于任何一條機器指令的取指令操作是相同的,是以将取指令操作的指令統一編成一個微程式,這個微程式隻負責将指令從主存單元中取出送至指令寄存器中,如圖2.1所示的取指周期微程式。此外,如果指令是間接尋址,其操作也是可以預測的,也可先編出對應間址周期的微程式。當出現中斷時,中斷隐指令所需完成的操作可由一個對應中斷周期的微程式控制完成。這樣,控制存儲器中的微程式個數應為機器指令數再加上對應取指、間址和中斷周期的3個微程式。

圖2.1 不同機器指令對應的微程式

2.微程式控制單元的基本框圖

如圖2.2所示,圖中點畫線框内為微程式控制單元,控制存儲器(控存)是微程式控制單元的核心部件,用來存放全部微程式;CMAR是控存位址寄存器,用來存放欲讀出的微指令位址;CMDR是控存資料寄存器,用來存放從控存讀出的微指令;順序邏輯是用來控制微指令序列的,具體就是控制形成下一條微指令(即後續微指令)的位址,其輸入與位位址形成部件(與指令寄存器相連)、微指令的下位址(簡稱“下位址”)字段以及外來的标志有關。

微指令基本格式如圖2.2下所示,共分為兩個字段,一個為操作控制字段,該字段發出各種控制信号;另一個為順序控制字段,它可以指出下條微指令的位址,以控制微指令序列的執行順序。

圖2.2 微程式控制單元的基本組成

3.工作原理

假設一個使用者程式如下所示,它存于以2000H為首位址的主存空間内:

LDA X

ADD Y

STA Z

STP

首先将使用者程式的首位址送至PC,然後進入取指階段。

(1)取指階段

①将取指周期微程式首位址M->CMAR;

②然後取微指令,将對應控存M位址單元中的第一條微指令讀到控存資料寄存器中,記作CM(CMAR)->CMDR。

③産生微操作指令,第一條微指令的操作控制字段中為“1”的各位發出控制信号,如PC->MAR,1->R,指令主存接收程式首位址并進行讀操作。

④形成下一條微指令的位址。下一條微指令位址為M+1,将M+1送至CMAR,即Ad(CMDR)->CMAR。

⑤取下一條指令。将對應控存M+1位址單元中的第二條微指令讀到CMDR中,即CM(CMAR)->CMDR。

⑥産生微操作指令。

由第二條微指令的操作控制字段中對應“1”的各位發出控制信号,如M(MAR)->MDR使對應主存2000H位址單元中的地一條機器指令從主存中讀出送至MDR中。

⑦形成下一條微指令位址。

(2)執行階段(執行LDA微程式)

①取數指令微程式首位址的形成。

OP(IR)->微位址形成部件->CMAR。

②取微指令。CM(CMAR)->CMDR。

③産生微操作指令。Ad(IR)->MAR,1->R。

④形成下一條為指令位址。Ad(CMDR)->CMAR。

⑤取微指令,CM(CMAR)->CMDR。

……

關鍵點:

(1)微指令的操作控制字段如何形成微操作指令;

(2)微指令的後續位址如何形成。

三、微指令的編碼方式(控制方式)

1.直接編碼(直接控制)方式

在微指令的操作控制字段中,每一位代表一個微操作指令。如下所示,下位址左側為控制信号,進行操作控制。速度最快。

| 下位址 |

2.字段直接編碼方式

将微指令的操作控制字段分成若幹段,将一組互斥的微操作指令放在一個字段内,通過對這個字段譯碼,便可以對應每一個微指令。這種方法靠字段直接譯碼發出微指令,又稱顯式編碼。它縮短了微指令字長,增加了譯碼時間。

圖2.3 字段直接編碼方式

3.字段間接編碼方式

一個字段的某些微指令還需要由另外一個字段的某些微指令來解釋,如圖2.4所示,圖中字段1譯碼的某些輸出受字段2譯碼輸出的控制,由于不少靠字段直接譯碼發出微指令,故稱為字段間接編碼,又稱隐式編碼。如圖2.4所示。

圖2.4 字段間接編碼方式

4.混合編碼

把直接編碼和字段編碼(直接或間接)混合使用。

5.其它

微指令中還可以設定常數字段,用來提供常數、計數器初值等。常數字段還可以和某些解釋位配合。

此外微指令還可以用類似機器指令操作碼的方式編碼。

四、微指令序列位址的形成

1.直接由微指令的下位址字段指出(斷定方式);

2.根據機器指令的操作碼形成;

3.增量計數器法;

4.分支轉移;

5.通過測試網絡形成;

6.由硬體産生微程式入口位址。

五、微指令格式

1.水準型微指令

一次能定義并執行多個并行操作。如直接編碼、字段直接編碼、字段間接編碼、直接和字段混合編碼等。

2.垂直型微指令

類似機器指令操作碼的方式。在微指令字中,設定微操作碼字段,由微操作碼規定微指令的功能。不強調其并行控制能力。

3.兩種微指令格式的比較

(1)水準型微指令比垂直型微指令并行操作能力強,靈活性強。

(2)水準微指令執行一條機器指令所需的微指令數目少,速度快。

(3)水準型微指令用較短的微程式結構換取較長的微指令結構,而垂直型微指令正好相反。

(4)水準型微指令與機器指令差别較大,而垂直型微指令與機器指令相似。

六、靜态微程式設計和動态微程式設計

靜态:微程式無需改變,采用ROM。

動态:通過改變微指令和微程式改變機器指令,有利于仿真,采用EPROM。

七、毫微程式設計

微程式設計用微程式解釋機器指令;毫微程式設計用毫微程式解釋微指令。

八、串行微程式控制和并行微程式控制

微程式指令也分為兩個階段:取微指令和執行微指令。串行微程式控制如下所示:

| 取第i條微指令 | 執行第i條微指令 | 取第i+1條微指令 | 執行第i+1條微指令 |

并行微程式控制增加了一個微指令寄存器來暫存下一條指令,以防止影響本條微指令的執行。如下所示:

| 取第i+2條微指令 | 執行第i+2條微指令 |

由于執行本條微指令與取下一條微指令是同時進行的,是以當遇到需要根據本條微指令的處理結果來決定下條微指令的位址時,就不能并行操作,此時可以延遲一個微指令周期再取微指令。