上拉電阻和下拉電阻二者共同的作用是:避免電壓的“懸浮”,造成電路的不穩定。

一、上拉電阻如圖所示:

1、概念:将一個不确定的信号,通過一個電阻與電源VCC相連,固定在高電平;

2、上拉是對器件注入電流,灌電流;

3、當一個接有上拉電阻的IO端口設定為輸入狀态時,它的常态為高電平。

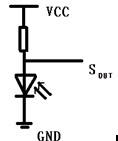

二、下拉電阻如圖所示:

1、 概念:将一個不确定的信号,通過一個電阻與地GND相連,固定在低電平;

2、下拉是從器件輸出電流,拉電流;

3、當一個接有下拉電阻的IO端口設定為輸入狀态時,它的常态為低電平。

三、小應用:

1.對于一些高輸入阻抗的電路,引腳懸空容易受到外界的幹擾(即使是很低的能量耦合至電路),此時設定上下拉電阻提供了一個相對低阻的通路。因為在低阻上産生一定的電壓所需的能量是比高阻的情況大得多的,這就減少了一部分能量較弱的幹擾信号的影響,降低受幹擾的機率。

2.對于COMS輸入,為防止靜電擊穿,設定一個上或下拉電阻,提供一個相對的低阻回路,以洩放存儲的電荷,不讓電壓積累。

3.對于高速電路,傳輸線效應開始顯現,設定上下拉電阻主要用以阻抗比對,減少反射,保證電平能夠被正确讀寫。

4.加上下拉電阻确定電平狀态,輸入或輸出可能存在偏流,設定上下拉電阻使偏流流經電阻産生一固定的狀态的偏置電壓。

對于輸入來說,偏流極小,即使懸空高阻下可能會有相對較大的輸入電壓,且不穩定,加下拉,偏流流過電阻産生的壓降仍極小,可認為将輸入電平确定為低。

對于輸出來說,通常針對的是集電極(漏極)開路(OC)的情況,加上拉電阻确定輸出電壓的變動範圍。

上述的情況也不過是普遍上的一種描述,真正上下拉電阻的作用還是得根據具體的問題進行分析,有的時候加個上拉也許隻會為了獲得與其他部件不同的微量的延遲,難以窮舉。多在實踐中分析和體會吧。

我的GitHub位址:

https://github.com/heizemingjun我的部落格園位址:

http://www.cnblogs.com/chenmingjun我的螞蟻筆記部落格位址:

http://blog.leanote.com/chenmingjunCopyright ©2018 黑澤明軍

【轉載文章務必保留出處和署名,謝謝!】