本節書摘來自華章計算機《高性能科學與工程計算》一書中的第1章,第1.1節,作者:(德)georg hager gerhard wellein 更多章節内容可以通路雲栖社群“華章計算機”公衆号檢視。

在1975~1995年的“舊時代”的科學計算時期,先進的高性能系統是專門為hpc市場設計的,主要的廠商有cray、cdc、nec、fujitsu和thinking machines等。在性能和價格方面,這些系統遠遠超越了标準的“商品”電腦。20世紀70年代初發明的單晶片通用微處理器,是20世紀80年代末唯一足夠成熟、可以打入hpc市場的技術。直到20世紀90年代末,标準的工作站叢集甚至基于pc的硬體至少在理論峰值性能上才具備相應的競争力。如今,情況已經發生了很大變化。hpc世界被低成本、現成的處理器系統占領,這些系統并不是主要為科學計算而設計的。一些傳統的超級計算機廠商在這個有利可圖的市場上活動,他們提供在單cpu水準上的高應用性能以及高度并行工作負載的系統。是以,科學家和工程師很可能遇到這樣的“商品模式”,即随着需求的增長推動硬體向更為專業的方向發展。是以,本章将主要關注基于标準的高速緩存微處理器的系統。向量機(vector computer)支援不同的程式設計方式,這種程式設計方式在很多方面更接近科學計算的要求,但是目前向量機已非常罕見。然而如果沒有它們,對超級計算機體系結構的讨論将不完整,1.6節對此提供了相關的概述。

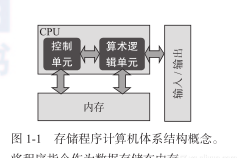

當讨論計算機系統時,我們的腦海中總是有一個清楚的體系結構概念,即1936年由圖靈提出并由eckert和mauchly實作的第一個真正的計算機edvac [c129,c131]。圖1-1顯示了存儲程式數字計算機的簡圖,将指令作為資料存儲在記憶體,這是它不同于早期設計的最大特征。指令由控制單元讀取并執行,一個獨立的算術邏輯單元根據指令來負責實際的計算并操作記憶體中的資料。通過i/o裝置可以與使用者通信。中央處理單元(cpu)包括控制單元、算術邏輯單元、适合的記憶體接口和i/o接口。在存儲程式計算機上程式設計意味着修改記憶體中的指令,原則上這可以由另一個程式完成。編譯器就是一個典型的例子,因為它将c或fortran等進階語言翻譯成能夠在記憶體中存儲并能被計算機執行的指令。

這個簡圖是現今所有主流的計算機系統的基礎,但仍然存在一些固有問題:

必須連續不斷地向控制和算術邏輯單元提供資料,是以記憶體接口速度成為計算性能的瓶頸,這通常稱為馮•諾依曼瓶頸。在接下來的章節中,我們将展示如何利用體系結構優化和程式設計技術減弱這個瓶頸導緻的不利影響。盡管如此,這個瓶頸仍然是最嚴重的性能限制因素。

這種體系結構存在内在順序性,一條指令可能處理來自記憶體的一個或一組操作數。sisd(單指令單資料,single instruction single data)即為這種概念。如何修改和擴充使得它能夠以多種不同方式支援并行,以及這樣一個并行機如何能夠有效運用,同樣是這本書的主題。

盡管存在着這些缺陷,但沒有其他的體系結構概念能在将近70年的電子數字計算機中如此廣泛地使用。