本節書摘來自華章計算機《計算機系統:系統架構與作業系統的高度內建》一書中的第3章,第3.3節,作者:(美)拉姆阿堪德蘭(ramachandran, u.)(美)萊希(leahy, w. d.)著, 更多章節内容可以通路雲栖社群“華章計算機”公衆号檢視。

3.3.1 電路

組合邏輯 這種邏輯電路的輸出是輸入的布爾組合。也就是說,這裡沒有狀态(即記憶)的概念。這種電路由基本的邏輯門(and、or、not、nor、nand)組成。另一種認識這類電路的方式是,它們沒有從輸入回到輸入的回報。

考慮一個混合了許多麥克風的輸入并給揚聲器産生一個複合輸出的插線闆。揚聲器的輸出取決于接線闆選擇的麥克風以便産生複合聲音。這個接線闆就是一種組合邏輯電路的例子。在處理器的資料通路中能發現的組合邏輯電路包括多路複用器、解複用器、編碼器、解碼器和算術/邏輯單元。

時序邏輯 時序邏輯電路的輸出是目前輸入與目前狀态的布爾組合。除了組成組合邏輯電路的那些基本的邏輯門外,組成時序邏輯電路還需要一種稱為觸發器的記憶元件作為關鍵部分。

考慮一個車庫門開關控制電路。這個電路的輸入就是一個按鈕以及一些表示門開着還是關着的開關。電路的輸出是一個控制電機升高或降低車庫門的信号。動作的方向取決于門的目前狀态。是以,車庫開關門控制器是一個時序邏輯電路。處理器資料通路中的寄存器和記憶體也是時序邏輯電路的例子。

3.3.2 資料通路的硬體資源

處理器的資料通路包含了組合邏輯與時序邏輯元件。根據第2章中給出的lc-2200指令集,我們來确定資料通路需要哪些資源。

我們需要記憶體來儲存指令和操作數。我們需要算術/邏輯單元(alu)來執行算術/邏輯指令。我們需要寄存器堆,因為它是大部分指令集體系結構中操作的重點。絕大部分指令使用寄存器堆。我們需要程式計數器(以後簡稱為pc)來指向目前指令以及用于實作第2章中讨論過的分支跳轉指令。當一條指令從記憶體中取出後,它需要存儲在資料通路的某個地方,是以我們引入了指令寄存器(ir)來儲存指令。

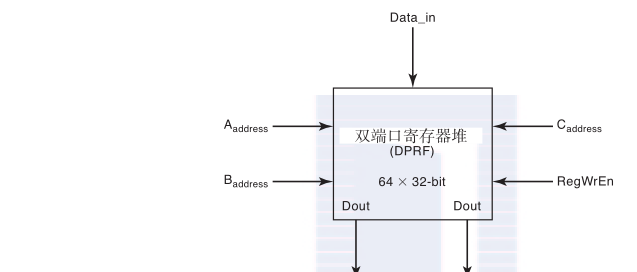

顧名思義,寄存器堆就是體系結構中程式員可見的寄存器的集合。我們需要控制線路和資料線路來操作寄存器堆。這包括用來尋找某一特定寄存器的位址線以及讀/寫寄存器的資料線。隻允許同時讀單個寄存器的寄存器堆稱為單端口寄存器堆(sprf)。允許同時讀兩個寄存器的寄存器堆,稱為雙端口寄存器堆(dprf)。例3-1給出了寄存器堆所需的所有控制線和信号線。

例3-1 下圖是一個雙端口寄存器堆(dprf),包含64個寄存器。每個寄存器32位長。aaddress和baddress是端口a和端口b所讀寄存器的位址。caddress是資料data_in寫入的寄存器的位址。regwren是寄存器堆的寫使能信号。圖中的每個箭頭各有幾根線?

答:

data_in有32根線。

端口a有32根線。

端口b有32根線。

aaddress有6根線。

baddress有6根線。

caddress有6根線。

regwren有1根線。

3.3.3 邊沿觸發邏輯

寄存器内容從目前狀态改變到新狀态是對時鐘信号的響應(見圖3-1)。

輸入變化引起輸出變化的具體時間取決于這個元件是電平邏輯還是邊沿觸發邏輯。在電平邏輯中,隻要時鐘信号是高電平,那麼變化就會發生。而在邊沿觸發邏輯(見圖3-2)中,變化隻會發生在時鐘的上升沿或下降沿。如果狀态變化發生在上升沿,則稱為正邊沿觸發邏輯;如果變化發生在下降沿,則稱為負邊沿觸發邏輯。

圖3-2 時鐘。時鐘周期指的是兩個連續的上升沿(或下降沿)之間的時間間隔

在後面的讨論中,我們假設資料通路中所有的寄存器都使用正邊沿觸發邏輯。我們将在3.4.2節中讨論選擇時鐘周期寬度的細節。

例3-2 寄存器a、b和c連接配接成了下面的電路:

lda、ldb和ldc是寄存器a、b和c的時鐘信号。如果在某個時鐘周期内a、b、c的值如圖中所示,那麼下一個時鐘周期它們的值又是什麼?

各個寄存器的輸入都将會變成它們的輸出,是以,

記憶體元件比較特殊(見圖3-3)。正如第1章中看到的,在讨論計算機系統組成時,實際上,記憶體子系統是完全與處理器分離的。然而,出于簡化處理器實作有關基本概念的目的,我們将記憶體包含在資料通路設計中。出于讨論的目的,我們認為記憶體不是邊沿觸發的。

例如,為了讀取某個記憶體單元,你給記憶體提供“位址”和“讀”信号,過了有限的一段時間(稱為記憶體的讀通路時間)後,該位址的内容就出現在“資料輸出”線上。同樣,為了寫某個記憶體單元,你提供“位址”、“資料輸入”,以及“讀”信号,在一段有限時間(寫通路時間)後,該記憶體單元的值就會變成通過“資料輸入”寫入的值。我們在第9章中會更詳細地讨論記憶體系統。

3.3.4 連接配接資料通路元件

讓我們考慮執行lc-2200指令集中的add指令需要什麼,并由此推出資料通路元件應該如何連接配接。

1)步驟1:我們需要pc來指明指令在何處(見圖3-4)。

2)步驟2:指令從記憶體中讀出後,就儲存到ir中(見圖3-5)。

3)步驟3:ir中的指令可用後,就可以使用(ir中的)指令中給出的寄存器号從寄存器堆(雙端口,與例3-1中的類似)中讀對應的寄存器。使用alu進行加法操作,并将結果寫回到寄存器堆中對應的寄存器(見圖3-6)。

圖3-6 步驟3。執行将兩個寄存器值相加并寫入第三個寄存器中

前面的3個步驟給出了add指令執行的路線圖。我們看看這三步能不能在一個時鐘周期内完成。前面提到,所有的存儲元件(除了記憶體外)都是正邊沿觸發的。這意味着,在一個時鐘周期内(如果相對于邏輯器件的延遲來說,時鐘周期足夠長的話),我們能将資訊從一個存儲元件傳送到另一個存儲元件(途中經過組合邏輯和記憶體)。是以,步驟1和步驟2可以在一個時鐘周期内完成。但步驟3不能在同一周期内完成。在步驟3中,我們需要從ir中将寄存器号取出傳送給寄存器堆。但由于ir的邊沿觸發特性,是以隻有到下一個時鐘周期後ir中的指令才可用(見圖3-7)。

事實證明,步驟3可以在一個時鐘周期内完成。在下一個時鐘周期開始時,ir的輸出可以用來索引需要從寄存器堆中讀出的具體的源寄存器。寄存器值讀出後(讀寄存器的過程與讀記憶體是類似的),将它們傳遞給alu,執行add操作,将結果寫入目的寄存器(由ir給出)。圖3-8闡明了步驟3在第二個時鐘周期内的完成情況。

決定時鐘周期 我們重新審視步驟1和步驟2,我們說過它們可以在一個時鐘周期内完成。要完成這些步驟,時鐘周期需要多長呢?根據圖3-7,從第一個上升沿開始,我們可以枚舉所有與這兩個步驟相關的組合邏輯的延遲:

等待pc輸出穩定到可以讀取的時間(dr-output-stable)。

pc輸出傳播到記憶體位址輸入的線延遲(dwire-pc-addr)。

讀取指定位址單元的記憶體通路時間(dmem-read)。

記憶體讀出值傳播到ir輸入的線延遲(dwire-dout-ir)。

在第二個時鐘上升沿前,ir的輸出需要達到穩定,這段時間稱為建立時間(dr-setup)。

在第二個時鐘上升沿後,ir輸出需要保持不變一段時間,這稱為保持時間(dr-hold)。

完成步驟1和步驟2所需要的時鐘寬度必須大于上述延遲的總和:

時鐘寬度> dr-output-stable + dwire-pc-addr + dmem-read + dwire-dout-ir + dr-setup + dr-hold

我們對每個時鐘周期内所有可能的信号傳播路徑進行分析。然後,令時鐘寬度大于整條路徑的最壞情況下信号傳播延遲。在3.4.2節中,我們将形式化定義計算時鐘周期涉及的術語。

例3-3 給出下面的參數(機關是皮秒(ps)),确定系統所需要的最小時鐘寬度(僅考慮前面所說的步驟1~3):

例子中的資料是相當準确的資料(2007年前後)。從例子中明顯可以看出線延遲占主要地位。

3.3.5 基于總線的設計

為了執行add指令,為資料通路上的元件建立了專門的連接配接。為了實作其他指令(如ld),我們需要建立一條從記憶體到寄存器堆的路徑。以此類推,我們可以想象資料通路上的所有元件都互相連接配接。事實證明,這沒有必要,也不是正确的方法。我們檢查連接配接alu到寄存器堆涉及什麼。我們需要與位寬相應數量的線路來連接配接兩個元件。對于32位的機器,需要32根線。當我們增加資料通路元件的連通性時,需要的線路就會快速增加。從占用矽片面積的角度來說,連線是非常昂貴的,是以我們需要減少連線數量以使矽片真正用于資料通路中活動的元件。而且,僅僅增加線路并不會帶來性能的提高。例如,從記憶體到寄存器的線路對于add指令的實作一點幫助都沒有。

是以,我們需要更加細緻地考慮資料通路元件的連接配接問題。具體來說,前面讨論給我們的啟發是,與其在每兩個元件之間連線,不如設計資料通路讓各元件共享線路。讓我們來研究需要多少線以及如何共享它們。

單總線設計 最極端的一種情況是,隻有一組總線,所有的元件都共享它。這就像小組開會一樣,一個人說,大家都在聽。如果有必要參與讨論,每個人都會輪到發言。如果同時有多人講話,當然就會很混亂。這就是單總線系統(一組線路被所有元件共享)的工作方式。圖3-9就是這樣一個系統。

圖3-9 單總線設計。僅有一個資料通路元件能夠将它的輸出放到總線上,這是通過相應的“驅動”信号來實作的

總線說明這組線路是共享。第一點需要注意的是,灰線是一條電氣單總線,也就是說,總線上的資料在總線的任意一段都是可用的。第二點需要注意的是,在元件和總線之間有些三角形。它們是驅動器(也稱為三态緩沖器)。每個元件需要連接配接到總線的輸出上,都會有這樣一個驅動器。它們将資料通路元件和總線進行電氣隔離。是以,為了“連接配接”元件1與總線,相應的驅動器必須是“開”的。這可以通過選擇相應的“驅動”信号來完成。然後,我們就說資料通路元件1在“驅動”總線。同時存在多個元件驅動總線是錯誤的。是以控制邏輯的設計者需要保證任意一個時鐘周期内僅有一個驅動器處于“開”狀态。如果多個驅動器同時處于“開”狀态,那麼除了總線上的值變得無法預測之外,還可能對電路造成緻命傷害。另一方面,總線上的元件在每個時鐘周期都會嘗試擷取總線上的資料。為此,元件上對應的wren(寫使能)信号必須為“開”。

雙總線設計 圖3-10展示了一個雙總線設計。在這個設計中,寄存器是雙端口的,類似于例3-1中的那樣。是以,在一個時鐘周期内可以同時讀兩個寄存器并傳送給alu。頂部的灰線和底部的黑色點線都是傳輸位址和資料值的總線,具體傳輸的内容取決于在這個時鐘周期内需要什麼。然而,在名義上,灰色總線傳輸位址而黑色虛線總線在元件之間傳輸資料。

雖然圖中沒有畫出,但在每個元件的輸出端都有驅動器連接配接到總線上。完成3.3.4節中的步驟1~3需要幾個時鐘周期呢?每個周期分别發生了什麼呢?

我們來探讨這兩個問題。

第一個時鐘周期:

從pc到灰色總線(注意:在這個周期内沒有其他元件能夠驅動灰色總線)。

從深灰色總線到記憶體位址。

記憶體讀取addr指定的單元。

資料從dout到黑色虛線總線(注意:此時沒有其他元件能驅動黑色虛線總線)。

從黑色虛線總線到ir。

時鐘觸發ir。

我們在一個時鐘周期内完成了步驟1和步驟2。

第二個時鐘周期:

ir将寄存器号提供給寄存器堆(見ir到寄存器堆的那個箭頭,它表示對應的線路),包括兩個源寄存器和一個目的寄存器。

讀寄存器堆,從兩個源寄存器中取出資料。

寄存器堆将兩個源寄存器的資料值提供給alu(見寄存器堆到alu的箭頭表示的線路)。

執行alu的add操作。

将alu結果提供給黑色虛線總線(注意,這個時鐘周期内沒有其他元件能夠驅動黑色虛線總線)。

從黑色虛線總線到寄存器堆。

根據ir給出的目标寄存器号,寫入寄存器堆。

在這個時鐘周期内我們完成了步驟3。

前面讨論中最關鍵的地方是,我們使用兩根共享總線(以及寄存器堆到alu的連接配接和ir到寄存器堆的選擇線路)而不是每一對元件間的專設線路完成了步驟1~3。

3.3.6 有限狀态機

目前為止,我們總結了電路元件以及它們如何組裝到處理器的資料通路中。這隻是處理器設計的一部分。處理器設計中同等重要的一部分是控制單元。最好将控制單元了解為一個有限狀态機(finiut state machine,fsm),因為将資料通路通過狀态切換來完成指令的執行。

有限狀态機,顧名思義,有有限個狀态。在圖3-11中,标記為s1、s2、s3的圓圈是fsm的狀态。箭頭則是狀态之間的轉移。fsm是任意時序邏輯電路的抽象。它描述了電路的行為。fsm的狀态對應着時序邏輯電路的某些實際的實體狀态。描述一個轉移的兩個參數是:1)觸發狀态發生變化的外部輸入;2)電路在狀态轉移中産生的輸出信号。是以,fsm描述實際電路所有硬體細節是很友善的。

例如,圖3-12中的簡單fsm就表示了之前介紹的車庫門開關控制電路。表3-1給出了這個fsm的狀态轉移表,包括導緻轉移的輸入以及産生的相應輸出。

狀态“打開”表示門是開着的,而“關閉”表示門是關着的。輸入是一個遙控器按鈕。輸出是控制馬達開關門的信号。标記為“0”和“1”的轉移表示是沒有按下按鈕的情況。标記為“2”和“3”的轉移則表示按鈕被按下。轉移“2”産生一個控制門升起的輸出信号,而轉移“3”産生一個使門降下的信号。學過邏輯設計課程的人都知道,給出fsm和狀态轉移表後,設計時序邏輯是一種很簡單的練習。(見本章末尾與車庫門開關控制器有關的兩道題。)

我們知道時序邏輯可以是同步的或異步的。對于前者,狀态轉移是與時鐘沿同步的,而後者的狀态轉移在輸入變化時就立刻發生。

處理器的控制單元也是時序邏輯電路。我們用圖3-13中的fsm表示控制單元。

fetch:這個狀态表示将指令從記憶體中取出。

decode:這個狀态表示對讀出的指令進行解釋以确定需要什麼操作數以及做什麼操作。

execute:這個狀态表示執行指令。

我們在3.5節中還會再講到控制單元。