本節書摘來自華章出版社《深入淺出dpdk》一書中的第2章,第2.1節存儲系統簡介,作者朱河清,梁存銘,胡雪焜,曹水 等,更多章節内容可以通路雲栖社群“華章計算機”公衆号檢視。

第2章 cache和記憶體

2.1 存儲系統簡介

一般而言,存儲系統不僅僅指用于存儲資料的磁盤、錄音帶和CD光牒存儲器等,還包括記憶體和cpu内部的cache。當處理完畢之後,系統還要提供資料存儲的服務。存儲系統的性能和系統的處理能力息息相關,如果cpu性能很好,處理速度很快,但是配備的存儲系統吞吐率不夠或者性能不夠好,那cpu也隻能處于忙等待,進而導緻處理資料的能力下降。接下來本章會讨論cache和記憶體,對于磁盤和錄音帶等永久性存儲系統,在此不作讨論。

2.1.1 系統架構的演進

在當今時代,一個處理器通常包含多個核心(core),內建cache子系統,記憶體子系統通過内部或外部總線與其通信。

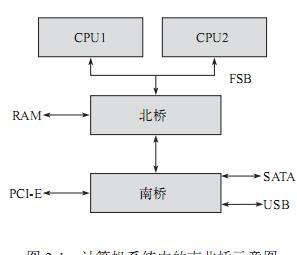

在經典計算機系統中一般都有兩個标準化的部分:北橋(north bridge)和南橋(south bridge)。它們是處理器和記憶體以及其他外設溝通的管道。處理器和記憶體系統通過前端總線(front side bus,fsb)相連,當處理器需要讀取或者寫回資料時,就通過前端總線和記憶體控制器通信。圖2-1給出了處理器、記憶體、南北橋以及其他總線之間的關系。

我們可以看到,該架構所有的處理器共用一條前端總線與北橋相連。北橋也稱為主橋(host bridge),主要用來處理高速信号,通常負責與處理器的聯系,并控制記憶體agp、pci資料在北橋内部傳輸。而北橋中往往內建了一個記憶體控制器(最近幾年英特爾的處理器已經把記憶體控制器內建到了處理器内部),根據不同的記憶體,比如sram、dram、sdram,內建的記憶體控制器也不一樣。南橋也稱為io橋(io bridge),負責i/o總線之間的通信,比如pci總線、sata、usb等,可以連接配接光驅、硬碟、鍵盤燈裝置交換資料。在這種系統中,所有的資料交換都需要通過北橋:

1)處理器通路記憶體需要通過北橋。

2)處理器通路所有的外設都需要通過北橋。

3)處理器之間的資料交換也需要通過北橋。

4)挂在南橋的所有裝置通路記憶體也需要通過北橋。

可以看出,這種系統的瓶頸就在北橋中。當北橋出現擁塞時,所有的裝置和處理器都要癱瘓。這種系統設計的另外一個瓶頸展現在對記憶體的通路上。不管是處理器或者顯示卡,還是南橋的硬碟、網卡或者光驅,都需要頻繁通路記憶體,當這些裝置都争相通路記憶體時,增大了對北橋帶寬的競争,而且北橋到記憶體之間也隻有一條總線。

為了改善對記憶體的通路瓶頸,出現了另外一種系統設計,記憶體控制器并沒有被內建在北橋中,而是被單獨隔離出來以協調北橋與某個相應的記憶體之間的互動,如圖2-2所示。這樣的話,北橋可以和多個記憶體相連。

圖2-2所示的這種架構增加了記憶體的通路帶寬,緩解了不同裝置對同一記憶體通路的擁塞問題,但是卻沒有改進單一北橋晶片的瓶頸的問題。

為了解決這個瓶頸,産生了如圖2-3所示的numa(non-uniform memory architecture,非一緻性記憶體架構)系統。

在這種架構下,在一個配有四核的機器中,不需要一個複雜的北橋就能将記憶體帶寬增加到以前的四倍。當然,這樣的架構也存在缺點。該系統中,通路記憶體所花的時間和處理器相關。之是以和處理器相關是因為該系統每個處理器都有本地記憶體(local memory),通路本地記憶體的時間很短,而通路遠端記憶體(remote memory),即其他處理器的本地記憶體,需要通過額外的總線!對于某個處理器來說,當其要通路其他的記憶體時,輕者要經過另外一個處理器,重者要經過2個處理器,才能達到通路非本地記憶體的目的,是以記憶體與處理器的“距離”不同,通路的時間也有所差異,對于numa,後續章節會給出更詳細的介紹。

2.1.2 記憶體子系統

為了了解記憶體子系統,首先需要解釋一下和記憶體相關的常用用語。

1)ram(random access memory):随機通路存儲器

2)sram(static ram):靜态随機通路存儲器

3)dram(dynamic ram):動态随機通路存儲器。

4)sdram(synchronous dram):同步動态随機通路存儲器。

5)ddr(double data rate sdram):雙資料速率sdram。

6)ddr2:第二代ddr。

7)ddr3:第三代ddr。

8)ddr4:第四代ddr。

1.sram

sram内部有一塊晶片結構維持資訊,通常非常快,但是成本相對dram很高,應用時容量不會很大,因而不能作用系統的主要記憶體。一般處理器内部的cache就是采用sram。

2.dram

dram通常是系統的主要記憶體,動态表示資訊是存儲在內建電路的電容器内的,由于電容器會自動放電,為了避免資料丢失,需要定期充電。通常,記憶體控制器會負責定期充電的操作。不過随着更好技術的提出,該技術已經被淘汰。

3.sdram

一般dram都是采用異步時鐘進行同步,而sdram則是采用同步時鐘進行同步。通常,采用sdram結構的系統會使處理器和記憶體通過一個相同的時鐘鎖在一起,進而使處理器和記憶體能夠共享一個時鐘周期,以相同的速度同步工作。該時鐘會驅動一個内部的有限狀态機,能夠采用流水線的方式處理多個讀寫請求。

sdram采用分布式架構,内含多個存儲塊(bank),在一個時鐘周期内,它能夠獨立地通路每個存儲塊,進而可以多次進行讀寫操作,增加了記憶體系統的吞吐率。

sdram技術廣泛用在計算機行業中,随着該技術的提出,又出現了ddr(也稱為ddr1),ddr2,ddr3。最新的ddr4技術标準也在2014年下半年釋出。