這一節将介紹直接通路存儲器(immediate access store)或者主存儲器(primary memory)。沒有低成本、高速的存儲器,實作複雜的作業系統和應用(例如photoshop)是十分困難的。本節首先介紹靜态存儲器(sram),因為它在動态存儲器(dram)之前出現且比dram更容易了解。實際上,cache存儲器通常由sram實作。

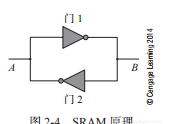

圖2-4說明了sram概念上是如何工作的。兩個反向器端端相聯構成一個環。門1的輸入是a,其輸出b=,這又是門2的輸入。門2的輸出是a,其中a===a,這也是門1的輸入。門1的輸入是由門1的輸入經過回報産生的。這是一個自主維持存儲器(self-sustaining memory)。無論初始給門1何種輸入,其回報都會使這種狀态得到維持。

圖2-5顯示了如何将圖2-4中的兩個交叉耦合的反向器變成實際的靜态存儲位元。作為開關的兩個半導體連接配接到反向器電路的左邊和右邊,用于通路存儲單元(右邊的陰影插圖顯示了半導體有3個端子;在控制栅極的信号電平決定了另外兩極之間的路徑是打開還是關閉)。當讀/寫信号線是低電平,這兩個半導體都處于打開狀态,資料信号線data和都沒有被反向器驅動(即被控制)。

資料寫入位元時,将要寫的一位資料及其取反值分别放在data和信号線上,然後發出讀/寫信号。反向器節點a和b被修改為所期望的值,當讀/寫信号為低電平時保持寫入的資料。當進行讀操作時,首先發出讀/寫信号,使反向器的輸出與資料信号線連接配接,然後讀取a節點的電平信号即可。

因為一個反向器需要由兩個串聯的半導體來實作,是以每個靜态位元需要6個半導體存儲一位資料。實際的靜态存儲器為m×n的位元陣列。通路位元時需要指定其行和列位址。是以,一個n位的靜态存儲單元需要6n個半導體加上用于行列位址解碼以及執行各種信号控制與保持操作所需的半導體。

有些靜态存儲器每個位元隻需使用4個半導體。無論怎樣,n位靜态存儲器位元需要4n或6n個半導體。而動态存儲位元隻需要一個半導體,這意味着動态存儲器的密度至少可以達到靜态存儲器的4倍。圖2-6給出了由6個半導體構成的靜态存儲位元的電路圖。圖中用插圖的形式将dram位元與其進行對比。靜态存儲器的速度比動态存儲器的速度要快。

半導體技術的進步總是在繼續。2001年,日本富士通實驗室的研究人員公布了一款由铟镓砷化物(與常見的半導體材料矽對比是一種很專業的物質)構成的單半導體靜态存儲位元的設計,可以工作在77k(-196℃)。這樣的溫度對目前的實際應用來說都太低。它可以通過量子隧道(quantum tunneling)效應來存儲資料。一些其他技術,如納米管,可能是未來高密度、低功耗存儲器的可能競争者。

一種實用的半導體sram晶片由獨立的存儲位元陣列構成。圖2-7給出了一個16位的存儲陣列(真正的靜态存儲陣列可能包含224個位元)。4位存儲器位址a0~a3被分為行、列位址。二–四譯碼器對兩位行位址進行譯碼後選中一行。

同時,列譯碼器選中4列之一。每行和每列的交叉處是存儲位元,根據信号的狀态進入讀或寫周期。這個陣列說明存儲器操作是以前面介紹的邏輯部件的形式進行的。存儲陣列的實際實作将使用圖2-6中所示的存儲位元。

下面來看看如何使用靜态存儲器。ram晶片被組織成一位寬、半位元組寬(4位)、位元組寬(8位)或16位寬的裝置。圖2-8給出了一個容量為512kb的sram,它有64k字,每個字8位。它有16條位址線a0~a15,可以選擇216=64k個位置,它還有8條資料線d0~d7可以在一個讀周期内将8位資料交給處理器,也可以在一個寫周期内從處理器接收8位資料。

通路sram之前需要在位址總線上給出一個位址,由一系列0和1的組合定義通路位置,然後要麼在讀周期中将資料交給資料總線,要麼在寫周期中從資料總線讀取資料。

sram的操作通過兩個信号和控制。決定了晶片是參加讀周期(=1)還是寫周期(=0)的操作。低電平有效的片選信号确定該晶片是參加讀或寫通路,還是保持空閑狀态。一般情況下,為高電平,此時信号被忽略。當為低電平時,晶片參與讀還是寫操作取決于信号。在讀周期中,可以控制存儲器三态緩沖器的輸出(參見《計算機組成原理》第2章)。

圖2-9給出了sram的時序圖(timing diagram),說明在讀操作期間事件發生的順序。時序圖表明,為保證正确的存儲器操作,信号必須保持的最小時間,并指出活動從開始到結束之間可能的最大持續時間。圖中帶箭頭的線表示因果系;例如,當在c點變低(原因)使資料總線驅動器在e點被打開(結果)。

假設最初(圖的左邊)為高,在整個操作期間保持1狀态。在圖2-9中沒有表示出來。

在圖2-9中的a點,位址總線通過改變狀态為目前讀操作提供一個有效位址。這種狀态的變化由位址線的交叉部分表示。一旦位址信号穩定下來,片選信号在c點指出開始進行存儲器通路。由于為高電平,故為讀操作周期。

為高與為低的效果導緻存儲器把資料放到存儲器的資料總線上。資料總線結束懸浮狀态,資料在e點開始出現在總線上。然而此時資料仍然是無效的,因為資料的通路時間尚未開始。

在f點,位址信号變為有效後,經過tacc秒,資料可以被處理器讀取。在d點,處理器将變成高電平以完成讀周期,在點g資料總線再次變成高阻的懸浮狀态。從b點改變位址到資料在g點發生變化的時間稱為資料保持時間(data hold time)。資料保持時間定義為位址和(或)控制信号發生改變後,資料總線上資料的保持時間。某些系統需要正的(非零)資料保持時間以保證資料可以被可靠地擷取。

圖2-10給出了一般的sram寫周期的時序圖,它比相應的讀周期更複雜(這情況對所有的儲存設備來說都存在)。每個晶片的具體實作不同,但基本原理是相同的。要存儲的資料先放到資料總線上,然後和變為低電平以啟動寫周期。

圖2-10中,位址總線在a點開始有效直到寫周期在b點結束。假定在c點變為低電平。此時,仍然為高電平,資料總線處于懸浮狀态。

通路在c點開始,但對ram而言,隻要為高電平就表示是讀周期。是以,在點g,ram開始用讀出的資料驅動資料總線。當然,此時的資料是無效的,因為資料的通路時間尚未開始。

在e點,處理器使變為低電平表明目前周期是寫周期。存儲器終止已經開始啟動的讀周期,并在點h停止用讀出的資料驅動資料總線。可見,存儲器在點g和h之間給出了假的資料。系統設計師必須保證,此時沒有其他裝置使用總線。

在點i,處理器将要儲存的資料放到資料總線上。寫周期的關鍵點為f點,此時信号的上升沿表示開始捕獲資料。資料必須在的上升沿之前有效,并保持到低電平變為高電平之後,此段時間為資料保持時間(data hold time)。真正sram的設計以或中的任何一個變為高電平來終止寫周期。

介紹完了sram,自然就應該介紹dram。但是在這之前,還應該順便介紹影響所有存儲器系統設計的兩個問題,無論是靜态/動态、讀寫/隻讀存儲器。這兩個問題就是位元組/字控制以及位址譯碼的使用。

20世紀70年代,微處理器都是按位元組寬度設計的,資料總線為8位寬。位址總線為16位,使用a15~a00這些位址線可以標明216=64k個位元組。當出現了16位處理器後,情況變得更複雜,此時需要通路位元組和16位的字(記住,存儲器是以位元組編址的,無論字長是1個、2個、4個還是多個位元組,都可以通路存儲器中的一個位元組)。

由于微處理器設計者既希望通路單個位元組又希望具有通路16位的能力,故他們實作了位元組控制機制允許通路單個位元組或者選中的字。一種典型的機制是使用位址總線選中一個16位的字(或32位或64位),然後使用位元組控制線(byte control line)選中該位址處的一個或多個位元組。圖2-11給出了一種可能的實作,通過位址線a15~a01來選中215個16位的字。

位址線a00沒有使用,因為每個位址總是選中兩個位元組;即位址為0,2,4,6,8,…,215。兩個位元組選通信号bs0和bs1控制選中字的奇數位元組還是偶數位元組,或者同時選中兩個位元組(參見表2-2)。

本節将簡介位址譯碼技術,它是将位址映射到處理器實體位址空間中的方式。這裡使用《計算機組成原理》第2章中的概念(二進制、十六進制以及簡單的邏輯)。因為位址譯碼多是嵌入式系統設計師而不是計算機設計師要考慮的事情,有些讀者可能希望忽略這部分内容。

在所有可能中最好的情況是,計算機具有n位位址總線可以通路2n個字,同時存儲部件有n位位址輸入和2n個存儲器位置。實踐中,實際系統可能有幾種不同的儲存設備連接配接到處理器的總線。如果計算機處理器有32位位址總線,可通路232個位元組,其存儲子產品(存儲器的基本元件為一個晶片,而存儲子產品是一個包含多個存儲晶片的電路闆)提供229個位元組(512mb)的存儲;即需要<code>232/229=23=8</code>個子產品來滿足處理器的空間需求。此時需要一種将存儲子產品的位址空間映射到處理器位址空間的方法。稱為位址譯碼器的電路用來檢測對特定存儲子產品的通路,一旦cpu産生的位址落在某存儲子產品的位址空間中,則将該子產品對應的信号變為有效。

圖2-12說明了為什麼需要位址譯碼。假設處理器使用位址線a00~a31通路4096mb的位址空間;即232=4096mb。該系統采用3個512mb的存儲子產品,每個子產品由位址線a00~a28通路。

圖2-13顯示了這3個512mb的子產品是如何映射到處理器的存儲空間中的。雖然已将子產品映射到存儲空間相鄰的區域,但沒有規定實體存儲器必須被映射到相鄰的塊。當然,如果存儲區域不連續,程式員或作業系統在加載程式和資料時就需要特别小心。子產品1配置設定的位址空間為0000 0000到1fff ffff,子產品2的為2000 0000到3fff ffff,子產品3的為4000 0000到5fff ffff。當然,每個512mb的塊都是由a00~a28通路。

圖2-14顯示了如何設計執行存儲子產品映射到處理器位址空間的邏輯。3個子產品中的每個子產品的29個位址線都與處理器a00~a28連接配接在一起。用從處理器那裡剩下的3根位址線a29~a31選擇某存儲子產品,即這些位址線産生的信号可以選中對應的存儲子產品。

第一塊存儲器512mb空間的位址為0000 000016至1fff ffff16。該子產品在a31a30a29=000時被選中。同樣,第二塊存儲器空間的位址為2000 000016至3fff ffff16,該子產品在<code>a31a30a29=001</code>時被選中。

這裡不再進一步探讨位址譯碼,因為這是系統設計者和電子工程師要考慮的問題。位址譯碼可以用來比對存儲部件和cpu的位址空間,它還可以做得更多。例如,可以在多個存儲器子產品之間實作切換來保證任務在實體上是彼此分離的(一種記憶體管理的形式)。

如果存儲器的通路時間為tacc,則不能減少其通路時間。但是可以通過交叉(interleaving)來減少有效存取時間(effective access time)。若某存儲位置在t0時刻開始通路,則資料在tacc時間後變為有效。在同一存儲子產品内另一個位置處的資料至少要再等tacc時間後才能擷取。但是,可以同時通路其他的存儲子產品;即并行通路多個存儲器子產品。

圖2-15說明了這種交叉的效果,圖中兩個存儲體并行排列。如果在t0時刻通路第一個存儲體,資料在tacc時間後變為有效。如果在<code>t0+tcyc</code>(其中tcyc為時鐘周期時間)時刻通路第二個存儲體,則第二個資料元素在<code>t0+tcyc+tacc</code>時間後有效。如果<code>tcyc<tacc</code>,則可以比在沒有交叉時更早地完成第二次訪存任務。隻有在一個存儲體通路資料時能夠産生另一個存儲體中操作數的位址時,有效的交叉才能實作。

存儲交叉技術被稱為低位交叉,其中存儲位址的低位用來選擇存儲體。假設處理器有32位位址總線和64位資料總線。位址位a03~a31用來選擇存儲器中的一個字,位址位a00~a02(通過位元組選通信号)用來選中目前字中的一個或多個位元組。使用位址位a04執行存儲體選擇,所有奇數号位址的資料字從一個存儲體中取出,而所有偶數号位址的資料字從另一個存儲體中取出。如果使用兩個位址位來實作交叉,則可以實作4個存儲體并行通路。在現代微機中,雙通道或三通道記憶體的原理同交叉的原理相同,允許同時通路2~3個dram存儲子產品。

下面将介紹dram的工作原理。通過幾代dram裝置的不斷發展,它們基于相同的基本工作原理,但使用不同的技術來降低平均通路時間。下面将介紹基本的dram,讨論其不同的變種,如頁模式dram、半位元組模式dram、edo存儲器、sdram和ddr dram。