目錄

- 【1】存儲器的層次結構

- 【2】存儲器的分類

- 【3】SRAM

- 1、基本原理:

- 2、結構:

- 3、晶片參數與引腳解讀:

- 4、CPU與SRAM的連接配接方式

- 【4】DRAM

- 1、基本原理:

- 2、結構

- 3、晶片引腳解讀:

- 【5】存儲器系統設計

- 【6】存儲器擴充設計(重點)

- 1、位擴充(位并聯法)

- 2、位元組擴充(位址串聯法)

- 3、位元組和位擴充

- 【7】片選信号産生(譯碼電路)(重點)

- 1、全位址譯碼

- 例題

- 2、部分位址譯碼

- 例題

- 3、線選譯碼方式

- 4、三種譯碼方式的比較

- 4、位址譯碼電路設計

- 步驟:

- 【1】基于74LS138專用譯碼器的設計

- 【2】基于74LS688比較器的設計

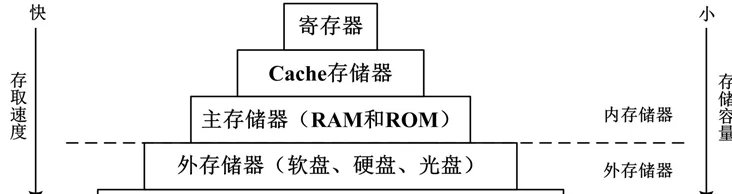

【1】存儲器的層次結構

【2】存儲器的分類

這裡我們揀SRAM和DRAM來講

【3】SRAM

1、基本原理:

靜态随機存取存儲器(SRAM):

所謂的“靜态”,是指這種存儲器隻要保持通電,裡面儲存的資料就可以恒常保持。

當電力供應停止時,SRAM儲存的資料還是會消失(被稱為volatile memory),這與在斷電後還能儲存資料的ROM或閃存是不同的。

2、結構:

⦁ 存儲矩陣,決定存儲器中存儲單元的排列形式,有字結構和位結構兩種

⦁ 位址譯碼器,用來選擇存儲單元,有線性譯碼和複合譯碼兩種,通常采用複合譯碼

⦁ 控制邏輯與三态資料緩沖器,控制CS、WR、RD信号

3、晶片參數與引腳解讀:

以6116(2K x 8)為例:

2K:表示該晶片内部存儲單元的數目,這個數決定存儲晶片位址線的數目。

8:表示該晶片每個存儲單元存儲資訊的位數,這個數決定存儲晶片資料線的數目。

引腳号如下:

4、CPU與SRAM的連接配接方式

注意:位址和控制BUS是單向指向存儲器,資料BUS雙向。

【4】DRAM

1、基本原理:

2、結構

⦁ DRAM的位址線是複用的,即位址線分為行位址和列位址兩部分。在對存儲單元進行通路時,由行位址選通信号RAS把行位址送入行位址鎖存器;再由列位址選通信号CAS把列位址送入列位址鎖存器

⦁ CPU與DRAM之間的資訊交換由DRAM控制器完成。

3、晶片引腳解讀:

【5】存儲器系統設計

所要考慮的問題:

1、總線的負載能力

2、CPU時序和存儲器存取速度之間的配合

3、存儲晶片的選擇以及數目

4、片内尋址和片間尋址位址線的配置設定

5、譯碼電路的選取(線性譯碼、全譯碼、部分譯碼)

6、資料線、控制線的連接配接

【6】存儲器擴充設計(重點)

1、位擴充(位并聯法)

⦁ 位擴充指用多個存儲器器件對字長進行擴充。一個位址同時控制多個存儲器晶片。

進行位擴充時,子產品中所有晶片的位址線和控制線互連形成整個子產品的位址線和控制線,而各晶片的資料線并列(位線擴充)形成整個子產品的資料線(8bit寬度)。

為何需要位擴充?

在微機系統中,存儲器是按位元組來構成的,而所選擇的存儲器晶片的字長不足8位

時,用這樣的存儲器晶片構成系統所需的存儲器子系統電路,就必須進行位擴充,即

用幾片存儲器晶片并起來,以增加存儲字長。例如上圖,兩個4位組成一個8位。是以稱為“位擴充”。

2、位元組擴充(位址串聯法)

⦁ 字擴充指的是增加存儲器中字的數量。

進行字擴充時,子產品中所有晶片的位址線、控制線和資料線互連形成整個子產品的低位位址線、控制線和資料線 , CPU的高位位址線(擴充的字線)被用來譯碼以形成對各個晶片的選擇線 —— 片選線

3、位元組和位擴充

1、首先對晶片分組進行位擴充,以實作按位元組編址;

2、其次設計個晶片組的片選進行字擴充,以滿足容量要求;

【7】片選信号産生(譯碼電路)(重點)

1、全位址譯碼

除了用于存儲器晶片片内位址外,CPU總線的其他位址總線都參加晶片的片選位址譯碼。

特點:

存儲器晶片隻占用整個存儲空間中的一塊區域,通路該存儲晶片片内單元采用唯一的位址。

例題

例:在8088CPU工作在最大方式組成的微機應用系統中,擴充設計8KB的

SRAM電路,SRAM晶片用Intel6264。若配置設定給該SRAM的起始位址為62000H~

63FFFH,片選信号(CS1) 為低電平有效。請用全位址譯碼方法設計該SRAM存儲器的

片選信号形成電路

分析:

1、Intel 6264

8K ×8位的SRAM

微機原理——擴充存儲器設計

2、8K ×8位:8KB,是以隻需要1片6264,不需要擴充

3、8086/8088CPU的位址總線均為20位,8086/8088CPU的尋址範圍為1MB; 8086有16根資料線和20根位址線,它既能處理16位資料,也能處理8位資料。可尋址的記憶體空間為1MB。

4、6264片内位址線有13根:A0~A12,是以CPU總線的低13位直接與片内位址引腳相連接配接,作為片内尋址,來選擇片内具體單元。

5、由于采用全譯碼方式,CPU高7位A19~A13全部參加譯碼。且晶片數量是1MB/8KB=128片。是以有128個片選位址。2^7=128.

62000H/2000H=49(10000H=8*2000H)轉換成二進制:0110001

6、片選信号是低電平有效,是以在位址譯碼設計中,若采用門電路,注意:A19~A13所有1進行邏輯與非,所有0進行邏輯或。

7、系統總線IO/M‘也參加譯碼

最終結果:

總結:…感覺步驟還挺多的,不過按照這個流程走一遍,第二次做的時候就很簡單了。

2、部分位址譯碼

也稱局部位址譯碼。片選信号不是由位址線中所有不在存儲器上的位址線譯碼産生,而是隻有部分高位位址線被送入譯碼電路産生片選信号。

特點:某些高位位址線被省略而不參加位址譯碼,簡化了位址譯碼電路,但位址空間有重疊。

例如,在8088 CPU組成的微機系統中,存儲器晶片采用8KB容量的6264晶片。在設計位址譯碼時,位址線A19未參加譯碼,隻有A13—A18 6條位址線參加譯碼。這時每塊6264将占有兩個8KB的記憶體空間。也就是說,記憶體空間發生了重疊現象,其重疊情況如圖6.23所示。從圖中可以看到,連接配接到記憶體空間最低8KB位址區的那一塊6264晶片,實際占有的記憶體位址空間為:00000H—01FFFH、80000H—81FFFH。它占有了兩個8KB的記憶體空間。可以依此類推,如果有兩條高位位址線不參加位址譯碼,那麼就會使4個存儲空間發生重疊; 3條高位位址線不參加位址譯碼,則會産生8個重疊空間。重疊空間數滿足下述關系:重疊空間數=2",其中,n為不參加位址譯碼的高位位址線。

例題

例:在8088 CPU工作在最小方式組成的微機應用系統中,擴充設計8KB的SRAM電路,SRAM晶片用Intel6264。若配置設定給該SRAM的位址範圍為00000H~0FFFFH,片選信号(CS)為低電平有效。請用部分位址譯碼方法設計該SRAM存儲器的片選信号形成電路。

分析:

1、6264的容量是8KB,然而00000H0FFFFH是64KB,是以重疊區域有64KB/8KB=8個,且2<sup>3=8,是以三條高位位址線不做譯碼,如A15A13

2、IO/M‘=0參加譯碼

3、線選譯碼方式

線選法:選擇除存儲器晶片片内尋址以外的高位位址線中的某一條,作為存儲器晶片的片選信号。

由于片選的位址線每次尋址時隻能有一位有效,不允許同時有多位有效,這才保證每次隻選中一個晶片或一個晶片組。

優點:選擇晶片不需要外加邏輯電路,姨媽線路簡單。

缺點:把位址空間分成了互相隔離的區域,且位址重疊區域多,不能充分利用系統的存儲器空間。

4、三種譯碼方式的比較

全譯碼:

系統所有位址線全部都應該參與譯碼

低段位址線應直接接在子產品上,尋址子產品内單元;

中段位址線譯碼後産生片選信号區分不同子產品;

高段位址線可用作片選信号有效的使能控制; 部分譯碼:

高端位址信号不參與譯碼,會造成位址空間的重疊和不連續 線譯碼;

電路結構簡單,但系統必須保證參與片選的位址線不能同時為有效電平;

同部分譯碼法一樣,因為有位址信号不參與譯碼,也存在位址重疊及不連續的問題 4、位址譯碼電路設計

步驟:

1、根據系統中實際存儲器容量,确定存儲器在整個尋址空間中的位置

2、根據所選用存儲晶片的容量,畫出位址配置設定圖,位址配置設定表

3、根據位址配置設定圖或配置設定表确定譯碼方法并畫出相應的位址位圖

4、選用合适期間,畫出譯碼電路

某微機系統位址總線為16位,實際存儲器容量為16KB,ROM區和RAM區各占8KB。其中,ROM采用2KB的EPROM,RAM采用1KB的RAM,試設計譯碼電路.

1、該系統的尋址空間最大為64KB,假定實際存儲器占用最低16KB的存儲空間,即位址為0000H3FFFH。其中0000H1FFFH為EPROM區,2000H~3FFFH為RAM區。

2、根據所采用的存儲晶片容量,可畫出位址配置設定圖;位址配置設定表

對于ROM來說每個子區域為2KB=2^11,需要11位位址線作為片内尋址:A0~A10;

對于RAM來說每個子區域為1KB=2^10,需要10位位址線作為片内尋址:A0~A9;

采用3—8譯碼器,前四根指向4片ROM,後四根加上一個A10構成二次譯碼,指向8片RAM;

【1】基于74LS138專用譯碼器的設計

引腳

真值表

例題1:在某 8088微處理器系統中,需要用8片6264構成一個64KB的存儲器。其位址配置設定在0000H~0FFFFH記憶體空間,位址譯碼采用全譯碼方式,用74LS138作譯碼器,請畫出存儲器譯碼電路。

分析:

1、6264片内位址線有13根:A0~A12,是以CPU總線的低13位直接與片内位址引腳相連接配接,作為片内尋址,來選擇片内具體單元。

2、由于采用全譯碼方式,CPU高7位A19~A13全部參加譯碼。且晶片數量是8片。

這裡我們隻是用A13~A15作為譯碼器的輸入,這樣正好有8種輸出。A16到A19作為選通信号3,全為0.

【2】基于74LS688比較器的設計

引腳

工作原理:

例:利用 74LS688設計譯碼電路,輸出端(P= Q)'作為Intel 62128 SRAM的CS片選信号,配置設定給Intel 62128的位址範圍為74000H~77FFFH。畫出8088 CPU工作在最大方式下的譯碼電路。

分析:

74000H轉換成2進制:0111 0100, 0000 0000 0000

77FFFH轉換成2進制:0111 0111 ,1111 1111 1111

觀察發現前6位都是一樣的,這樣就可以定位大的範圍,就可以确定Q的值了:101110(從低位到高位)

是以結果如下:

如果需要改變記憶體晶片的位址,隻需要改變Q那邊開關就行了。是以這種結構可以為改變記憶體位址帶來友善。

如果不需要改變位址,則可以直接給定Q邊的編碼就行了。

參考連結: