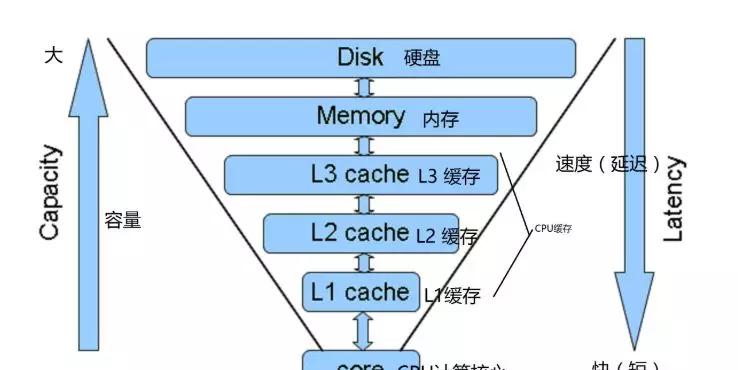

開局一張圖

由于CPU頻率太快了,為解決直接讀取記憶體的資料上的延遲,在CPU和記憶體之間,存在3級緩存。 CPU在解決和緩存不一緻上采用兩種方式:

- 緩存一緻性協定

- 總線鎖機制

CPU

CPU的一個時鐘周期指的是機器碼的0和1的變化,是電信号的一高一低的變化是10納秒左右,1s相當于10的9次方納秒。

市面上的緩存基本采用SRAM存儲器,可以不需要電路就能儲存内部資料,不像DRAM需要定時重新整理充電一次,不然資料會丢失。

是以SRAM具有更好的性能,但是缺點是體積較大,這也是不能将緩存容量做太大的原因。

為提高CPU的使用率,會增加多級緩存,但資料讀取和寫入都是在主存上進行的。

RAM

RAM(随機讀寫存儲器)工作原理大概是:

當cpu讀取主存時,将位址信号放到位址總線傳遞給主存,主存讀取位址信号後,解析信号,并定位到指定存儲單元,然後将存儲單中繼資料放到總線上傳回給CPU,這個慢展現在電信号打交道上。

磁盤的慢展現在他是需要借助磁頭移動的,這個尋址過程伴随着機械運動,是以就更慢了。

MESI

每個線程都有自己的緩存,這也往往造成多線程資料安全的問題。這時就需要一種協定保證緩存一緻性。

保證線程在讀取主存時遵循某種規則,保證不出現資料不一緻的問題,比較多的就是MESI協定。

MESI定義了cache line的四種狀态,線程對cache line的四種操作可能産生不一緻狀态。

- M:(modified 被修改) 某CPU緩存某個緩存行和主存資料的不一緻,該緩存行需要在未來某個時間點回寫主存,回寫之後狀态變為(exclusive 獨享)

- E:(exclusive 獨享)CPU緩存中的某個緩存行和主存資料一緻,處于這個狀态的可以被其他CPU讀取記憶體時變成(shared 共享),修改時變成(modified 被修改)

- S:(shared 共享)某緩存行可能被多個CPU緩存,并且各個緩存中的資料和主存一緻,當一個CPU修改該緩存行,其他CPU中該緩存行可以變成(invalid 無效)狀态

- I:(invalid 無效)該行是無效的(可能其他CPU修改了該緩存行)

當緩存控制器監聽到本地操作和遠端操作的時候,需要對位址一緻的cache line進行一緻性修改,保證資料在多個緩存之間一緻。 cache line可以根據MESI協定達到不同狀态之間的轉化,一個處于M狀态的緩存行必須時刻監聽所有試圖讀該緩存行相應的主存操作,必須該緩存行回寫主存并将狀态變成S才可以。

總線鎖

MESI協定之前,解決緩存一緻性方案是總線鎖機制,這種方案比較低效,鎖期間,其他CPU無法通路記憶體。

CPU亂序

多核時代,處理器為提高運算速度,可能作出違背代碼原有初衷的行為。 解決這種問題的方式就是記憶體屏障,簡單點說是不同的處理器架構提供了不同指令集用來建立記憶體屏障,這樣控制不可亂序。

版權聲明:本文為CSDN部落客「weixin_34159110」的原創文章,遵循CC 4.0 BY-SA版權協定,轉載請附上原文出處連結及本聲明。

原文連結:https://blog.csdn.net/weixin_34159110/article/details/92073461