除了輸入輸出端口,FPGA中還有另一種端口叫做inout端口。如果需要進行全雙工通信,是需要兩條信道的,也就是說需要使用兩個FPGA管腳和外部器件連接配接。但是,有時候半雙工通信就能滿足我們的要求,理論上來說隻需要一條信道就足夠了,而FPGA上實作這一功能的管腳就是inout端口。管腳相連時,input對應output,是以inout隻能和inout連接配接(否則就不是inout了)。本文将概述FPGA的inout端口。

1. 三态門

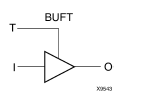

三态門,故名思議就是這個期間具有三種狀态。對于數字電路來說,三種狀态是高電平、低電平和高阻态。Xilinx的《XST User Guide》上給出了三态門的Verilog HDL(以及VHDL)的描述,具體如下:

1 // Tristate Description Using Concurrent Assignment

2

3 // Combinatorial Always Block Can be Used too.

4

5 module v_three_st_2 (T, I, O);

6

7 input T, I;

8

9 output O;

10

11 assign O = (~T) ? I: 1’bZ;

12

13 endmodule 三态門意味着,輸出端口除了輸出高、低電平之外還可以有第三種狀态,這是inout端口實作的基礎。

2. 高阻和懸空

三态門中有一個狀态是高阻。高阻,即可以認為是沒有輸出,作為輸出端口而言,對下級電路沒有任何影響。懸空是針對輸入端口來說的,也就是說沒有接輸入。這也就意味着,實際上高阻和懸空是一個狀态,在HDL語言裡都表示為Z。

也就是說,一個輸出端口在高阻态的時候,其狀态是由于其相連的其他電路決定的,可以将其看作是輸入。

3. INOUT

從上一節内容中可以看出,當三态門的輸出處于高阻狀态的時候,取值由外部電路決定,也就是說,這一時刻是可以作為輸入。INOUT端口的描述和示意圖如下

1 module inout_def(clk,data_inout)

2 input clk;

3 inout data_inout;

4 reg data_out;

5 reg data_out_control;

6 //define data_out

7

8 //define data_out_control

9

10 //assign data_inout

11 assign data_inout=data_out_control?data_out:1'bz;

12

13 //assign data_in

14 wire data_in;

15 assign data_in=(!data_out_control)&data_inout;

16

17 endmodule 4. PULLUP和PULLDOWN

如果兩個INOUT都處于高阻态,那麼接收到的信号到底是什麼狀态呢?這實際上等效為兩個INPUT端口連接配接,也就等效為INPUT端口懸空。

這應該是取決于外圍的驅動,添加的上拉或者下拉電阻,一般而言,FPGA添加的是上拉電阻,也就意味着此時chipscope采集的資料是高電平.

FPGA管腳内部可以配置弱上拉或下拉電阻來實作Z狀态下的控制。分别采用PULL UP和PULL DOWN限制實作,UCF、NCF文法如下

1 NET "pad_net_name" PULLUP;

2

3 //Configures the I/O to use a Pullup constraint.

4

5 DEFAULT PULLUP = TRUE;

6

7 //Configures the Pullup constraint to be used globally. 這一部分内容有待進一步驗證。

自由轉載,轉載注明出處(http://www.cnblogs.com/sea-wind/)

姓名标示(BY)-相同方式分享(SA)