學習目标

1. 了解ISA抽象的作用

2. 掌握ISA,并能舉一反三學習其他體系結構

3. 了解流水線和實作方式

學習任務

1. 閱讀教材,完成課後練習(書中有參考答案)

4.1-4.3中練習,重點:4.1 4.2 4.5 4.6 4.8 4.10 4.11 4.12 4.16 4.17 4.19 4.21 4.24

2. 考核:練習題把資料變換一下

3. 實驗:需要動手的到實驗樓中練習一下

第四章處理器體系結構

ISA:一個處理器支援的的指令和指令的位元組級編碼稱為它的指令集體系結構

ISA在編譯器編寫者和處理器設計人員之間提供了一個概念抽象層,編譯器編寫者隻需要知道允許哪些指令,以及它們是如何編碼的;而處理器設計者必須建造出執行這些指令的處理器

4.1 Y86指令集體系結構

l 程式員可見狀态:Y86程式中的每條指令都會讀取或修改處理器狀态的某些部分。“程式員”既可以是用彙編代碼寫程式的人,也可以是産生機器級代碼的編譯器。

l Y86指令集 :這些指令其實就是IA32指令集的子集

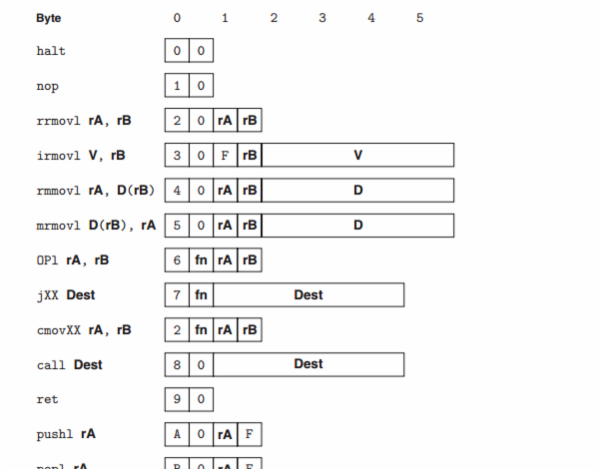

l 指令編碼:每條指令的第一個位元組表明指令類型。這個位元組分為兩部分,每部分4位:高四位是代碼部分,低四位是功能部分。有的指令隻有一個位元組長,而有的需要操作數的指令編碼更長。可能有附加的寄存器訓示符位元組。有些指令需要一個附加的四位元組常數字。指令集的一個重要性質就是位元組編碼必須有唯一的解釋。

l Y86異常:Y86有四種不同的狀态碼,AOK(正常)、HLT(執行halt指令)、ADR(非法位址)和INS(非法指令)。當Y86遇到異常,我們就簡單地讓處理器停止執行指令。

l Y86程式:有的時候Y86需要兩條指令來達到X86一條指令就可以達成的目的。

4.2邏輯設計和硬體控制語言HCL

l 邏輯門:AND => && Or => || Not => !

l 組合電路和HCL布爾表達式:很多邏輯門組成一個網。邏輯門的輸出不能連接配接在一起。必須無環。多路複用器:根據輸入控制信号的值,從一組不同的資料信号中選出一個。

l 存儲器和時鐘:為了産生時序電路,也就是有狀态并且在這個狀态上進行計算的系統,我們必須引入安位存儲資訊的裝置,儲存設備都是有同一個時鐘控制,時鐘是一個周期性信号。

4.3 Y86的順序實作

l 将處理器組織成階段:

取指:從存儲器讀取指令位元組,位址為程式計數器的值。它按順序方式計算目前指令的下一條指令的位址valP。

譯碼:從寄存器檔案讀入最多兩個操作數,得到值valA和/或valB。

執行:算數/邏輯單元要麼執行指令指明的操作(根據ifun的值),計算存儲器引用 的有效位址,要麼增加或減少棧指針,得到的值稱為valE。在此也可能設定條件碼,對一條跳轉指令,這個階段會檢驗條件碼和分支條件。

訪存:可以将資料寫入存儲器,或者從存儲器讀出資料,讀出的值為valM。

寫回:最多可以寫回兩個結果到寄存器檔案。

更新PC:将PC設定成下一條指令的位址。

以上階段無限循環,指導遇到異常。我們想使硬體數量盡可能的少,一種方法是讓不同指令共享盡可能多的硬體。

實驗五: